Summary and conclusion

So what can we really deduce from the results? At least the first step shows that the supposed minimum values from Intel and JEDEC are apparently only theoretical values and that the performance scales well above or below them in practice and does not drop off immediately. To what extent Intel’s hybrid memory controller with DDR5 and DDR4 pin compatibility is responsible for this will probably only become clear with the first DDR5-only CPU generation later this year.

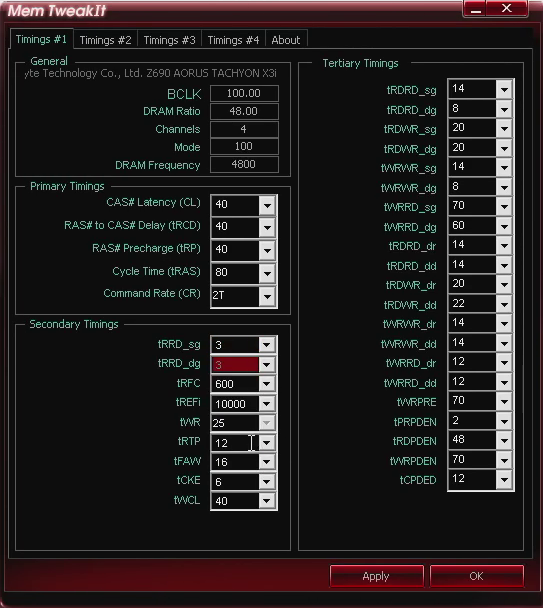

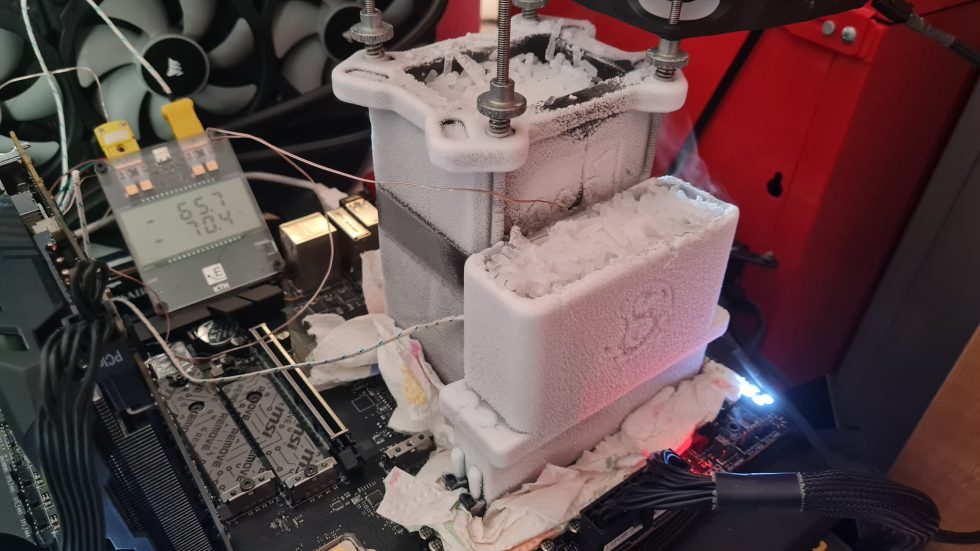

The Activate timings tRRD_S, tRRD_L, tFAW and tRTP have the property in common that if the value is too low, the system does not immediately crash or become unstable, as is the case with many other timings. Here it is now worthwhile to go beyond the specified limits and really test to what extent the performance scaling can actually be measured. Incidentally, I also verified the behavior with DDR5-6200 and with much tighter subtimings, with very similar results.

Of course, performance gains in the per mille range are uninteresting for the vast majority of gamers and even enthusiasts, but especially for overclockers looking for the last few points in benchmarks, one or two useful insights might have revealed themselves today. Often it’s only a few points that separate the top places in the rankings from each other and, as we all know, many small improvements add up quickly.

Feel free to let me know if this technical dive into the world of DDR5 timings was interesting and somewhat understandable. Ideas for tests on further timings and an efficiency comparison of different motherboard manufacturers with identical timings already exist. I will probably also do those tests anyway out of personal interest, just whether you think they are worth another post on Igor’s Lab, please let me know.

Bisher keine Kommentare

Kommentar

Lade neue Kommentare

Artikel-Butler

Alle Kommentare lesen unter igor´sLAB Community →