Some of my articles mature like old wine and it’s certainly not wrong to look at them from time to time, even with current references. This is especially true now with regard to the current “drama” surrounding Intel’s CPUs and the move with the specs for the baseline. Nobody can pretend that Intel didn’t know anything about this, because they simply changed the specs between 2021 and 2023. I’ll cautiously call it the “Ryzen effect”. And of course I can also think of a classic that I can’t include here audiovisually for licensing reasons, but the quote should actually suffice:

Pippi Longstocking

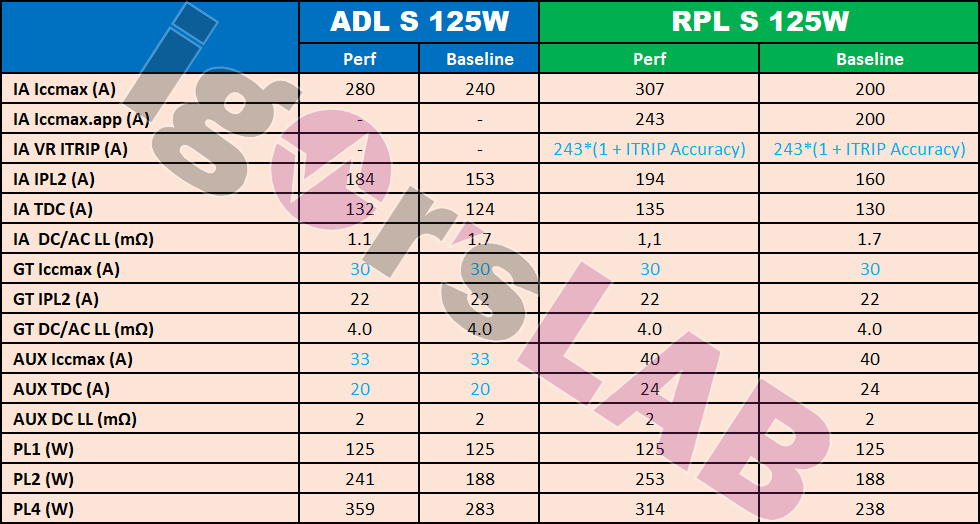

That’s exactly what happened with Intel’s specs, only in technical terms. In case anyone (doesn’t) remember, I had already leaked the key data of Intel’s Alder Lake S and Raptor Lake S in August 2021 and also listed data there that no longer appears in the normal specs that were later made public. That is, if they are still available at all. That’s also a strange thing. After all, in 2021 there was no sign of such nice gimmicks as PL1 = PL2 in performance mode and values over 188 watts in the baseline for the PL2.

Well, and then the Ryzen effect just mentioned came into play and with it the energetic Intel pressure refueling. The good old foie gras sends its regards. But it must also be emphasized at this point that arguing solely with the PL2 for the baseline is still far too nebulous. Until October 2022, i.e. the launch of Raptor Lake, the 188 watts for the PL2 were also set in the baseline. And that’s exactly where Gigabyte has corrected this value again with its current BIOS.

But the performance setting had already been set at 253 watts in 2021. The fact that PL1 = PL2 came directly at the launch of Raptor Lake S at the end of October, even if it was not in the October 2022 document. The whole thing was confusing for many. Especially as the results of the benchmarks differed from one another when switching between the three performance or cooler profiles “Boxed”, “Tower” or “AiO” and the values for PL1 and PL2 were always set to the same value manually afterwards (e.g. 125 / 188). So more must have happened than just changing PL1 and PL2.

We can see very clearly in the first table from the 2021 table that the PL4 of Raptor Lake S is significantly lower (in theory). However, this is a value that Intel is reluctant to make public and I will have to come back to it in a moment. Intel’s IMPV9.1 (Intel Mobile Voltage Positioning) also comes into play in all these discussions, where the processor voltage (VCC) is dynamically adjusted based on processor activity to reduce the power consumed. This enables a higher processor clock frequency for a given power consumption or a lower consumption for a given clock frequency, depending on the case. In my opinion, however, this was only finalized after the launch of RPL S.

New features include support for two VID tables with 5 mV and 10 mV resolution and support for Iout with values above 255 amps. There is also an analog AUX-Imon input on the 0x0Dh domain. There is also a change to the fast Psys counters and peak detector to support both Psys and Vsys measurements independent of the old Psys ADC input. IMPV9 was already a big step forward in the 10th generation compared to IMPV8, which we still know from the CPUs of the 9th generation.

The “mysterious” PL4

Things like Processor Pmax, Never Exceed and Limit are calculated “a priori” and are therefore a genuine PROACTIVE limit value (the result itself is planned and achieved through differentiated advance planning and targeted interventions). PL1 and PL2 only refer to the average performance and are REACTIVE limits, where only values can be reacted to retrospectively. The mysterious PL4 refers to peak power events, which before Alder Lake and Raptor Lake could only be handled proactively and often never turned out to be completely optimal in the end.

A new, REACTIVES PL4, on the other hand, is the ideal solution from Intel’s point of view, in which the SoC frequencies remain as high as possible, but with a safety net based on Fast PROCHOT#. This is a digital output pin that has been around since Intel’s Pentium 4 processors and indicates that the internal thermal control circuit has been activated. This happens when the processor has reached its maximum safe operating temperature. However, the SoC frequency is still determined by the PL4.

When PROCHOT# is enabled, the total power of the SoC is always BELOW PL4_Safe, i.e. lower than the value set for the PL4. PL4_Safe therefore represents the level of peak power that the input power sources can deliver without fear of overloading the power supply (VRM) and the other components connected in between. Fast PROCHOT# is really fast. Vsys1 is monitored by the IMPV9.1 controller and PROCHOT# is activated within 2 μs (adjustable) after the threshold is exceeded. The CPU is then throttled 1μs later. Fast PROCHOT# thus enables a higher PL4, which leads to better responsiveness down to low load states while maintaining system stability, but also generates harder load changes.

However, one of the most important pieces of information is the interval of PL4. Here, this state can last up to 10 ms, but never longer. But it is not written anywhere how long the pauses between these high load states must be.

The Potential Peak Power (PPP)

The PPP is an expected worst-case power level calculated by the Power Control Unit (PCU) based on the component characteristics and the current operating frequency (IA, GT, ring domains). This occurs before each frequency transition (usually at 1-ms boundaries), or whenever AVX commands enter the pipeline or a core C state change is imminent. PPP assumes a scenario across domains, which is the most intensive known application.

So what does this mean in the context of the PL4? Quite simply: the PL4 is the limit value to which PPP is ultimately compared! If PPP at the frequency transition is > PL4, a lower frequency is selected to prevent PPP from exceeding PL4. Incidentally, PPP is purely a projection and is NOT based on the power telemetry of the current workload. The PPP projection is also not displayed via a software interface, but is only used within the CPU.

The absolute peak performance can therefore only be reduced preventively via the PL4 settings. Of course, I can only speculate, but the current problems are certainly also the result of the unfortunate exaggeration of the PL4 and thus the PPP as well as the previous degradation of the CPUs due to overly optimistic default settings.

Comparison with the current status

The earliest document I have with the current, significantly higher values of PL1 and PL2 is revision 2.5 from February 2023 and already contains the Extreme Config, which did not exist before. This will then continue unchanged until revision 3.5 from December 2023:

It is also interesting in this context that there are no officially available explanations or readout options for the PL4 values that are currently actually implemented, whereby 420 watts are assumed for the K models of the I9. However, it can be assumed that these have been adjusted in the new BIOS from Gigabyte, for example, in parallel to the 188 watts for the PL2, which was originally in the Intel specifications at 314 watts. Anyone who has the right hardware and can therefore read out and compare the values from the first table in the BIOS will certainly be able to determine this. However, this also means that Intel alone is probably to blame for the current situation. Because what is not released will not be implemented by the board manufacturers.

Intel had already committed itself to Arrow Lake S. According to the latest (unofficial) information, the TDP is 125W, which is standard for unlocked CPUs from Intel. The PL2 rating of 177 watts is significantly lower than that of the Core i9-13900K and 14900K (currently rated at 253W), which means a 43% reduction in power consumption. The situation is similar with the PL4 power limit, which is said to be set at 333W. If we now take the reported PL4 limit of 420W, this would correspond to a 26% reduction. This is of course purely speculative, but it also shows that Intel is (or was) well aware of the problems with the PL4 and thus the PPP, which cannot be changed directly.

Here once again the link to my article from Saturday, which also contains my leak of Intel’s internally distributed preliminary report:

Intel veröffentlicht das „13th and 14th Generation K SKU Processor Instability Issue Update“

106 Antworten

Kommentar

Lade neue Kommentare

Mitglied

Urgestein

Urgestein

Mitglied

1

Urgestein

1

Veteran

Mitglied

Neuling

Mitglied

Veteran

Veteran

Urgestein

Veteran

Urgestein

Mitglied

Urgestein

Veteran

Alle Kommentare lesen unter igor´sLAB Community →