tRTP (tRDPRE) in benchmarks

The default setting for the tests with tRTP are again the Activates with 8/8/32, so that the influences of the timings can be isolated from each other. The baseline for tRTP is 12, which is the minimum adjustable value on many motherboards. And also below the Intel Spec down to 0 the value is set again in the OS, if possible. Also, tRTP and tRDPRE are used synonymously in the following.

Unlike the Activates, an increase in performance is only really visible in the Memory Score, albeit only in the range of about 35 points, compared to about 120 between the Activate settings. The memory score is also included in the total score, but other run to run variances seem to partially drown it out. As with the Activates, however, the performance here again scales well below the specified minimums of JEDEC and Intel down to 0.

Unlike the Activates, an increase in performance is only really visible in the Memory Score, albeit only in the range of about 35 points, compared to about 120 between the Activate settings. The memory score is also included in the total score, but other run to run variances seem to partially drown it out. As with the Activates, however, the performance here again scales well below the specified minimums of JEDEC and Intel down to 0.

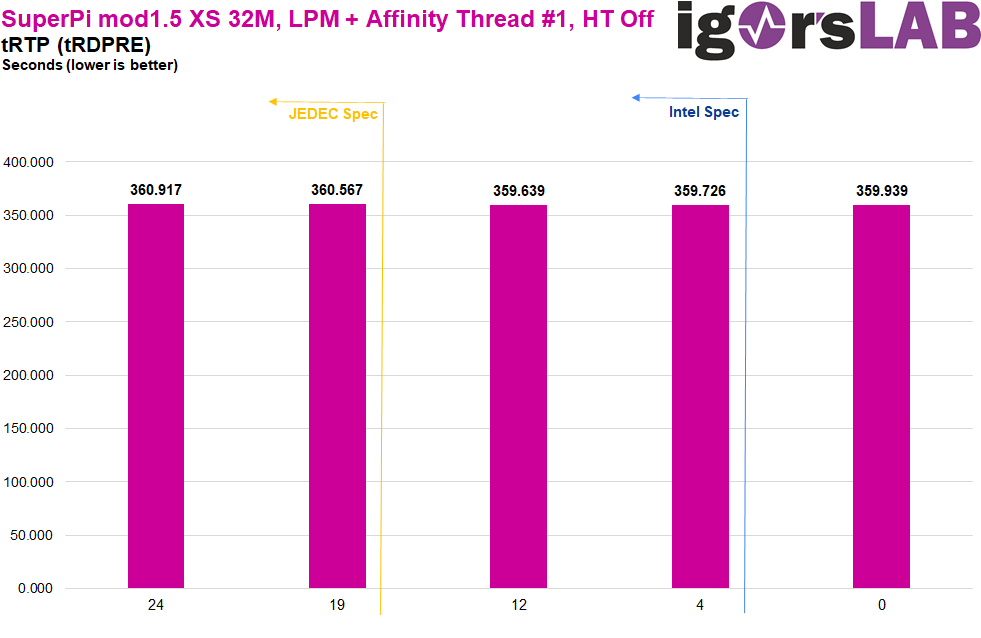

The SuperPi 32M is the first time the picture is completely different, with the best result in the middle of our test series at tRDPRE 12, with 0 and 24 being almost half a second slower. Even though these differences are within the variances of individual runs, the average is confirmed to be exactly the same after dozens of runs. DDR5 is known to have an integrated OD ECC (On-Die Error Correction Code), which could explain the slight performance regression when tRDPRE is too tight and in the extremely latency-sensitive SuperPi, but it could as well be within error of our measurements.

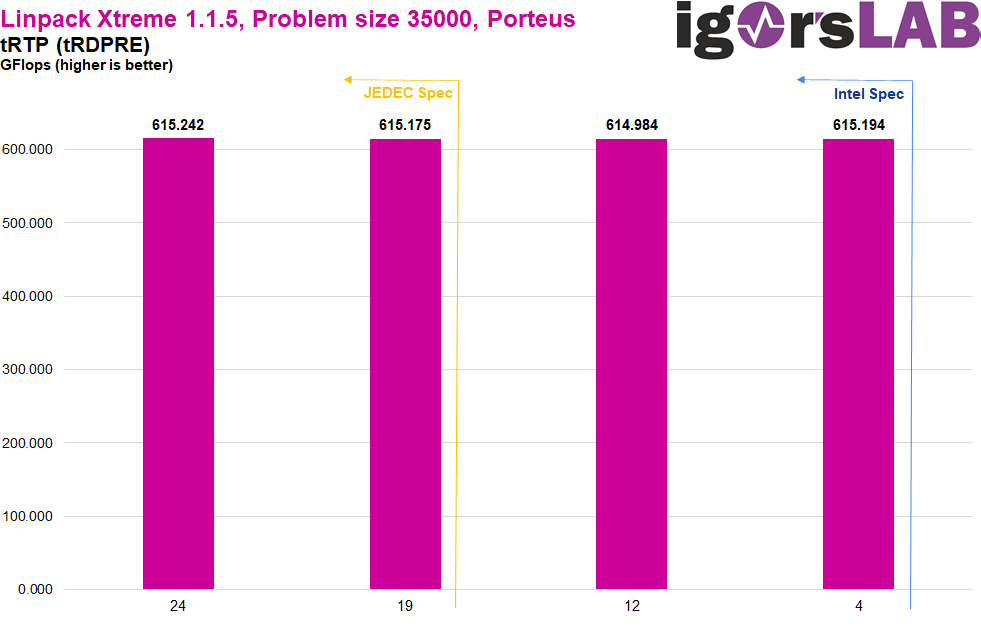

Linpack is again only available within the Intel spec due to the already explained technical limitations with the operating system. In fact, the fastest setting here is tRDPRE 24, followed by 4 and 19. There is no real ranking here, so I’ll leave the results as they are.

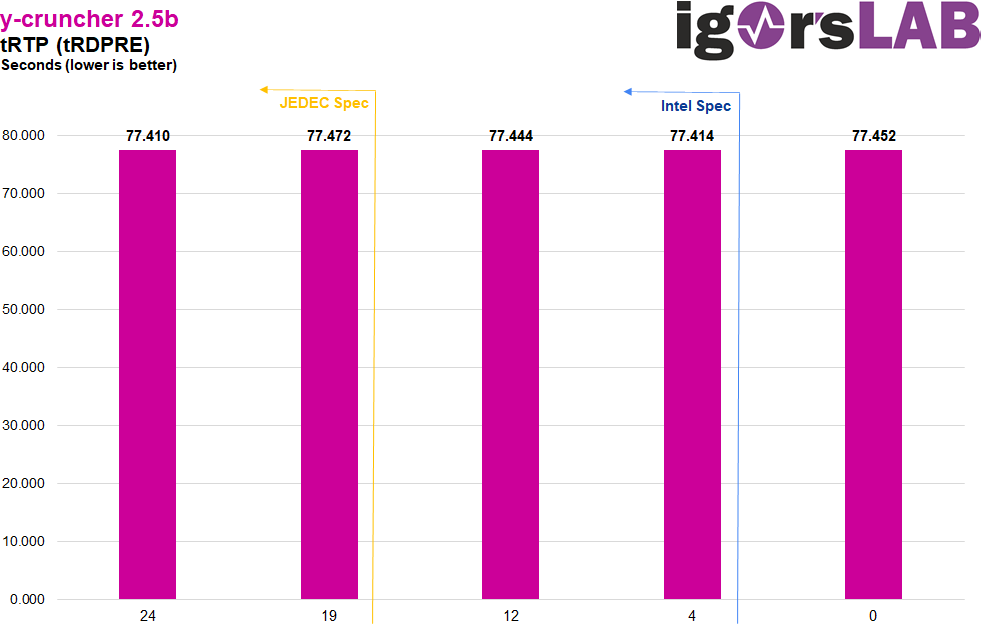

Interestingly, for the y-cruncher, tRDPRE 24 is also the fastest, followed closely by 4. However, to the best of my knowledge and belief, I cannot deduce a regularity from the measurement results here. It would be theoretically possible that values divisible by x are particularly suitable for timings, due to interactions with other subsequent timing operations, but it is not reliably measurable. In the end, this is only the data after several days of tests and over 40 test cycles, and I would write off the similarity in timing value 24 of the two benchmarks as a coincidence.

Bisher keine Kommentare

Kommentar

Lade neue Kommentare

Artikel-Butler

Alle Kommentare lesen unter igor´sLAB Community →