Memory latency, L3 cache, and intercore

All latency tests are performed with the latest version of sisoftware Sandra Titanium 2018. The developer recently stated that AMD did not report any measurement issues in these tests. Nevertheless, it is important to enjoy the results with caution, as the Zen-2 architecture and chiplet structure are still very new.

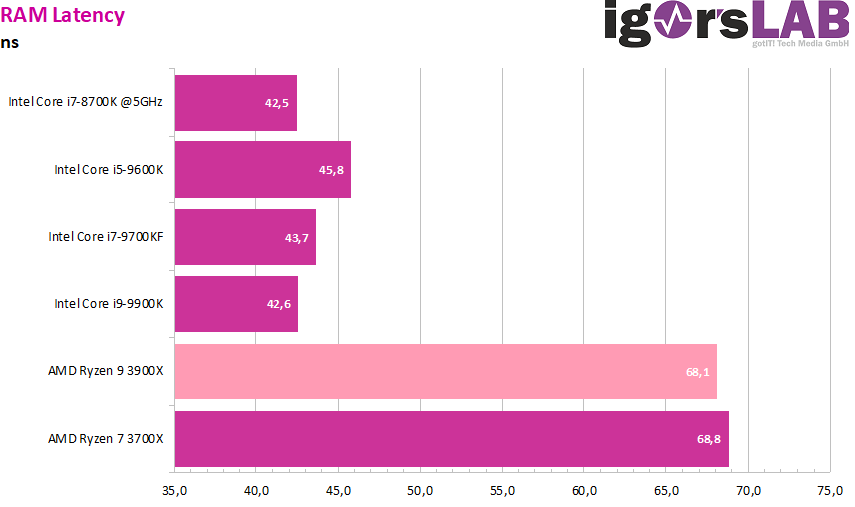

RAM latency (ns)

If the memory bandwidth of the two Ryzen CPUs is at or above this level, the communication latency between the CPUs and the respective DRAM on Intel systems is 50% higher. The Ryzen draws the shortest here. This is also quite understandable, since this communication has to run during ryzening via the input/output chiplet, which represents the connection between the CPU chiplet and the DRAM.

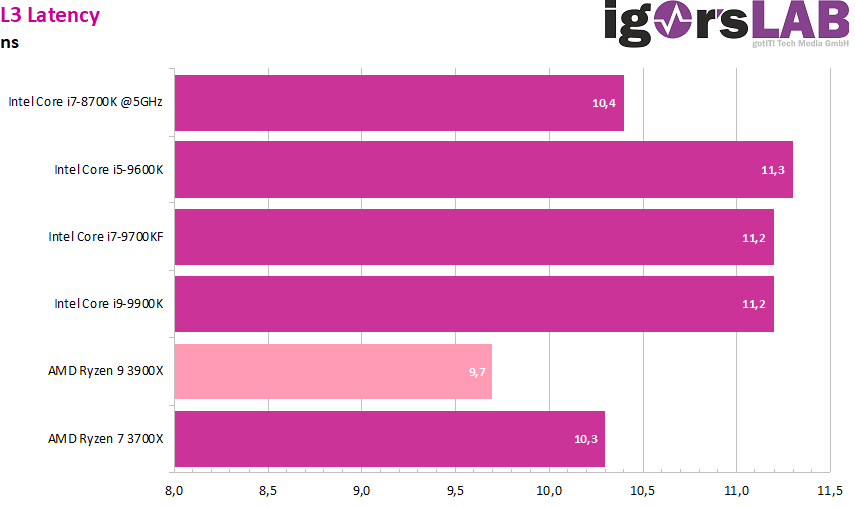

Cache latency L3 (ns)

The L3 cache is still as efficient as ever with the new Ryzens CPUs. Zen 2 cores access the cache faster than Intel Prozssoren. Only after overclocking to 5 GHz is the speed reasonably balanced. It should be pointed out again that L3 cache is abundant – 32 MB for 8 cores. AMD has put a lot of effort into optimizing cache memory and the investment seems to be paying off.

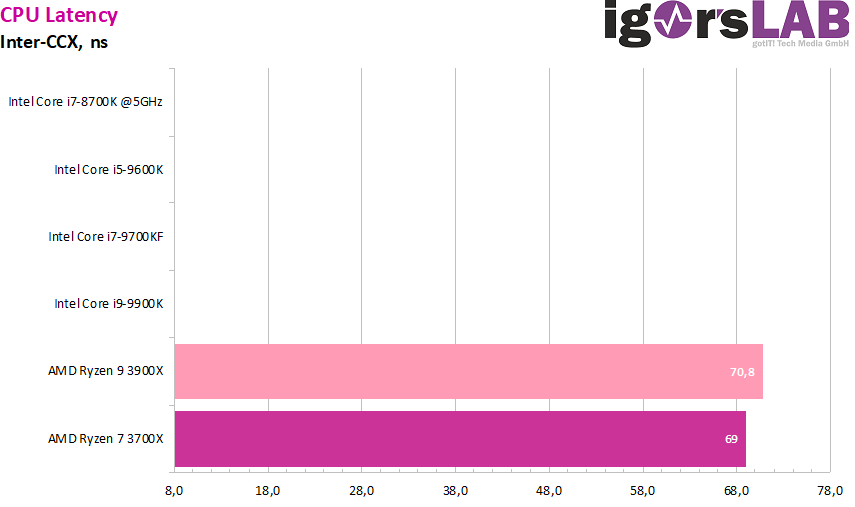

Inter-core and inter-CCX latency times

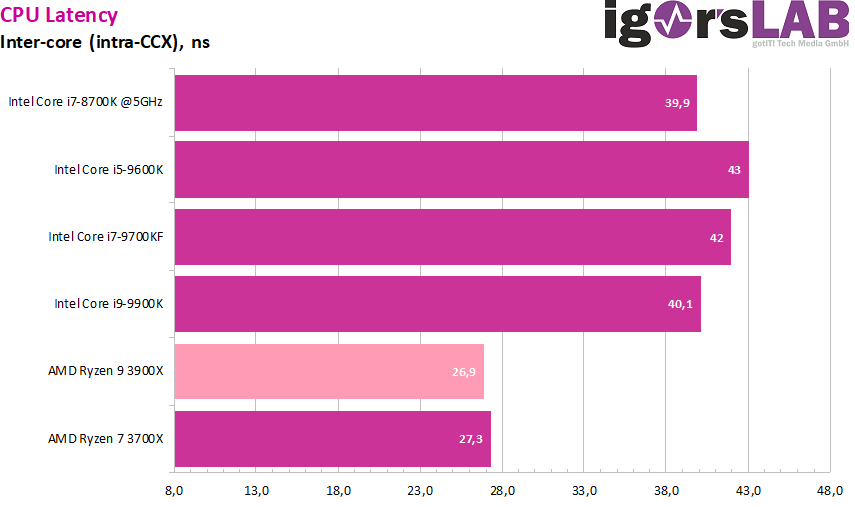

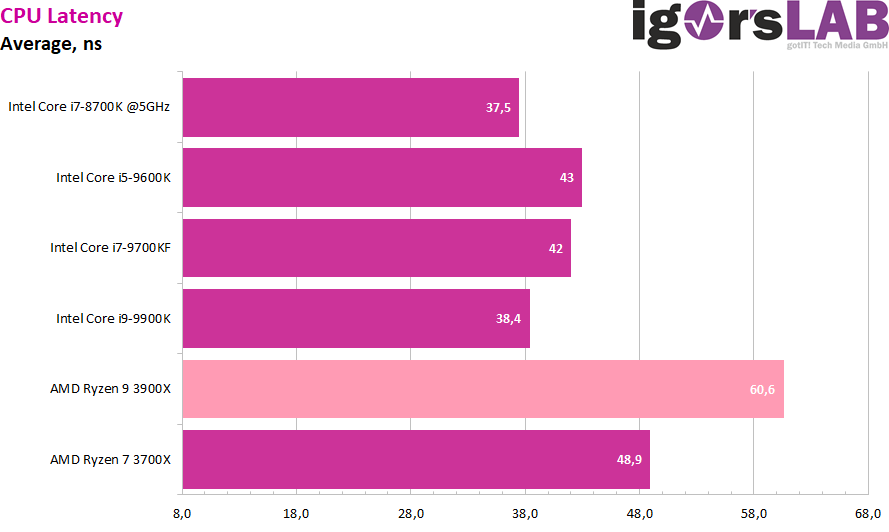

Intel CPUs continue to communicate quickly between the different CPU cores, but AMD can make up a lot of ground with the new Ryzen generation. In fact, the average latency of the Ryzen processors is clearly determined by the high, logically inter-CCX latency of the Ryzens at 70 ns – but constant, even between the chips, as everything goes through the Infinity Fabric.

Intel does not have this problem, thanks to a unified structure between all cores. For intercore latency (between the nuclei) and intracore latency (between the vCPUs of each hyperthreaded core), the Ryzens are much faster. Especially between the cores, this implies the good functioning of the L3 cache memory of the Ryzen CPUs.

The following diagrams continue to list all CPUs from the test field – even if they do not support inter-CCX or multithreading from their technical structure.

- 1 - AMD Ryzen 3900X und 3700X

- 2 - Straßenpreise

- 3 - Schneller DRAM

- 4 - Speicherbandbreite und L3-Cache

- 5 - Speicherlatenzen, L3-Cache und Intercore

- 6 - 4 Leistung: H.265-Kodierung

- 7 - Leistungsmerkmale: 3DMark TimeSpy

- 8 - Leistung in Spielen

- 9 - Leistung: Frametimes

- 10 - Leistung: SPECviewperfs 13

- 11 - Leistung: SPEC Workstation

- 12 - Leistungsaufnahme

- 13 - Fazit

Kommentieren