Regular readers have known me as an overclocking maniac for quite some time now and won’t be surprised that I don’t only test our Chinese oddball with the clocks intended by Intel. Because even if the multiplier of the chip is locked – no “K” suffix in the product name – a bug in an early microcode allows the total clock to be increased via the base clock (BCLK).

Thus, the BCLK governor’s limit of 102 MHz can be bypassed by motherboards with an external clock generator. Asus were the first to implement this loophole as an option on their Z690 Maximus boards in the BIOS. Accordingly, I use my Maximus Z690 Apex today to once again significantly increase the clock of cores and cache.

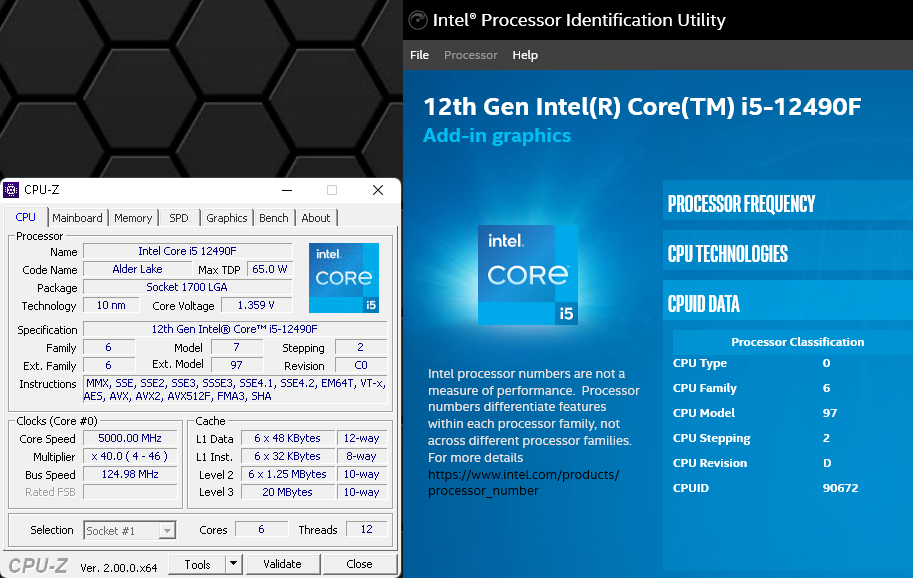

For this, the option “Unlock BCLK OC” has to be enabled in the “Extreme Tweaker\Tweaker’s Paradise” menu, which effectively loads an alternative microcode at the next system start, which contains or can exploit the above-mentioned gap. This can then also be recognized in the “Advanced\CPU Configuration” menu at “Microcode Revision D”, where the previously loaded version was 18, in the case of my BIOS 9902.

Now the multipliers for cores and cache have to be set statically to the highest that the CPU allows – in this case 40 for the specified 4.0 GHz all-core boost. And just now the clock can be increased as a product of multiplier and BCLK via the latter to the desired value, e.g. here with 125 MHz to 5.0 GHz. The BCLK screw cannot be turned without limitations, but it still goes far enough for condensation-free cooling solutions.

Now you just have to take in to account that the multiplier of the cache/ring and the divider for the RAM are also multiplied by the BCLK and that they have to be adjusted accordingly. Thus, DDR5-6000 becomes 6750 here. Power, of course, always comes from fuel, so naturally the voltage and load line calibration must be raised to an appropriate level. For 5.0 GHz on the cores and 4.875 GHz on the cache, my chip is happy with 1.35 V and LLC4 and thus just under 1.20 V under full load.

A higher clock rate is of course also possible, assuming a corresponding cooling solution or lower stability standards. With my 360 AIO and Prime95 Small-FFTs, however, it already stops at just over 5 GHz. Pleasant side effect of the microcode loaded for BCLK OC: AVX512 is active. We’ve already covered the “secret” instruction set and its efficiency advantages over the officially supported AVX2 to death in the past. Intel has now completely deactivated this for Alder Lake chips produced in 2022, while we can still make use of it here with a specimen from 2021 and thus increase the efficiency.

8 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Moderator

Urgestein

Veteran

Mitglied

Urgestein

Urgestein

Veteran

Alle Kommentare lesen unter igor´sLAB Community →