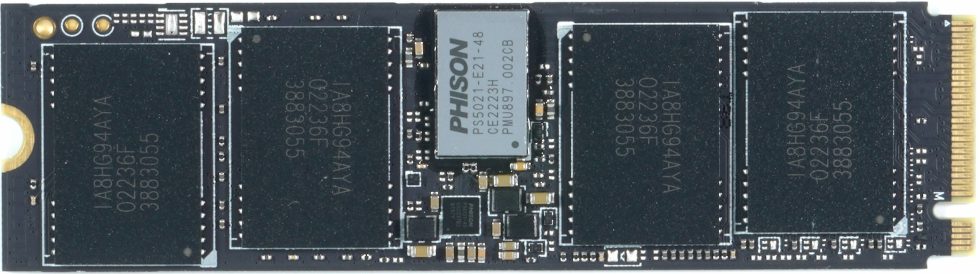

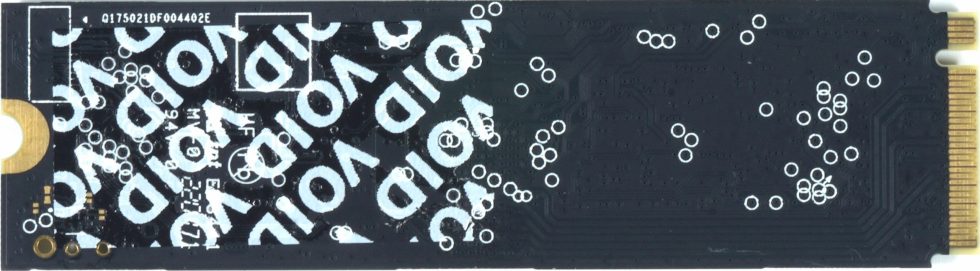

I had already written that the stickers should be removed for a good performance, because the 4 to 5 watts peak (measured) at maximum load want to be dissipated well on both sides. Once you have done that, you can see the PCB, which again comes from TECHVEST, but has been customized and also assembled by Corsair. In contrast to the faster models, the MP600 GS no longer uses the Phison E18, but it deliberately relies on the smaller and more economical Phison E21T.

This has only one core (ok, there are three in total together with the co-processor) and with four NAND channels also only half of the Pro XT. Furthermore, the SSD has to do without a dedicated DRAM cache and instead accesses the computer’s normal system RAM via host memory buffer (from Windows 10). You can definitely do that, because normally even this standard NVMe feature is enough to compensate for the lack of a dedicated DRAM cache.

The controller communicates with the NAND via four NAND flash channels with up to 1,600 MTps and supports capacities of up to 4 TB with 16 chips. Our sample contains four modules (Micron B47R, 8 dies at 512 Gigabit each) on one side, which can easily fit thanks to the small size of the controller. However, as already mentioned, the design no longer uses a DRAM-based architecture. There would have been no more room either. Thus, in the tested 2 TB model, there are 32 of these 512 GB flash chips in the form of Micron’s new 176-layer NAND (B47R), which all work at the same speed of 1,200 MTps in this model.

The chips installed are a quad-plane replacement gate architecture that uses metal-based control gates and some other design and production optimizations to increase performance and endurance. MSI still uses Micron’s 96-layer B27B in the SPATIUM M480. By the way, the next picture shows what happens when you remove the sticker in a cold state:

The Phison E21T complies with the NVMe 1.4 specification and has a number of common features. Thus, it supports both Trim and S.M.A.R.T.. Like other controllers, it uses Active State Power Management (ASPM), Autonomous Power State Transition (APST), and the L1.2 ultra-low power state (see data sheet page 1). Thermal throttling is implemented, but is of no further concern since the controller does not get too hot in most applications. This can also be seen in the fact that, unlike the older models like the E16, you can do without an integrated nickel heat sink.

It also leverages the fourth-generation LDPC ECC engine, SmartECC (RAID ECC), and end-to-end data path protection for robust error correction and improved data reliability. It even supports hardware-accelerated AES 128/256-bit encryption (which is TCG, Opal 2.0, and Pyrite compliant) and has a built-in crypto-erase feature. Like the E12S and E16 models, Phison’s E12T supports fully dynamic write caching. The size of the dynamic pSLC cache, which I will discuss in a moment, is therefore a maximum of 1/3 of the available capacity of the TLC drive. Phison has also implemented SmartFlush, which enables fast cache recovery for predictable and consistent performance. So much for the theory. Well, not quite.

What does dynamic pSLC cache actually mean?

Let’s move on to a more technical detail, which most people might not be aware of to its full extent. Much has already been written about pSLC cache, so there is no need to go through it again in detail, at most as a small refresher. Here we go…

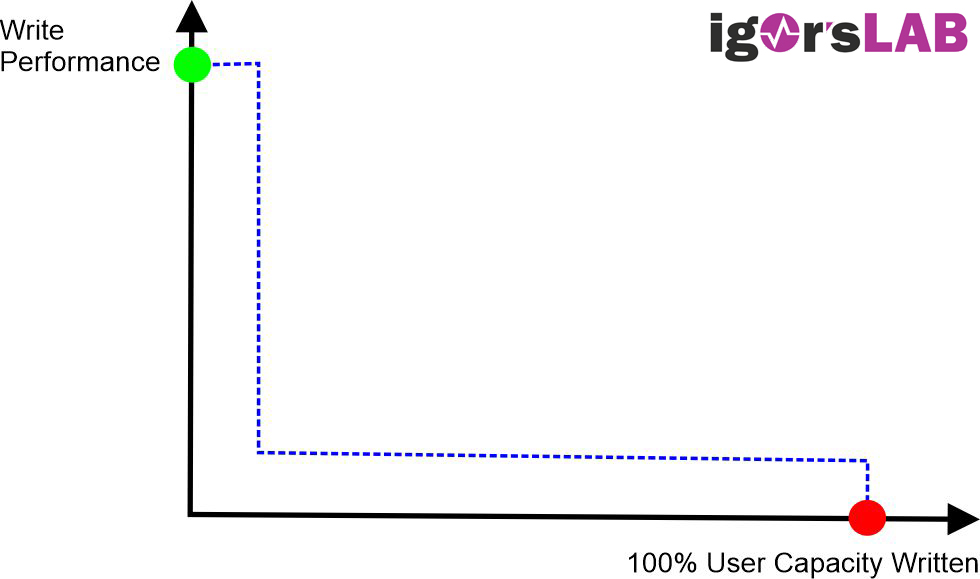

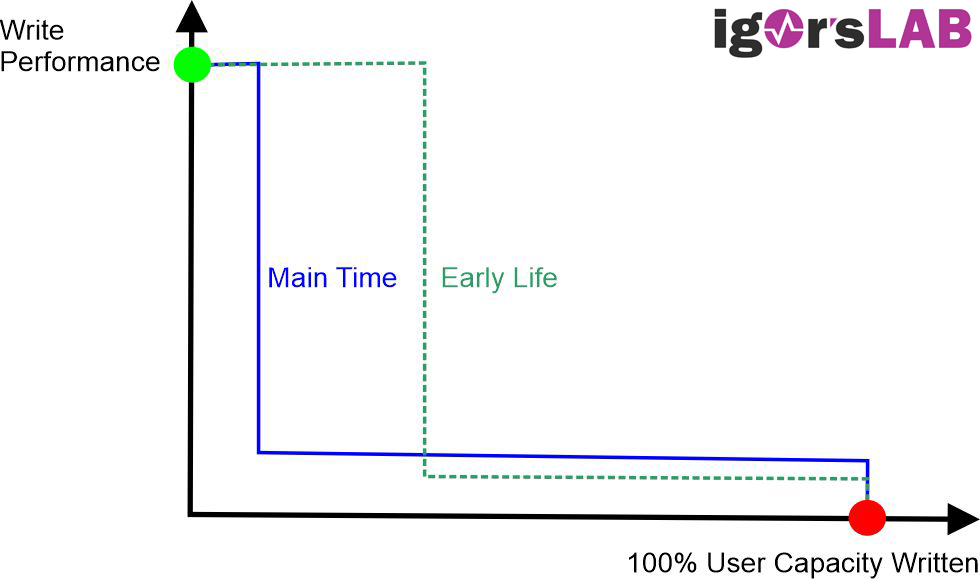

To increase the write speed, the so-called “pseudo-SLC cache” (pSLC) is often used in consumer products, although it can now also be found in various industrial solutions. For this purpose, part of the NAND capacity is configured as SLC memory, in which only one bit per cell is stored. Accordingly, this memory can be written and read very quickly. Since it is not dedicated, i.e. not a real SLC memory, it is called pseudo SLC. Such a cache can be used for all memory types that store several bits per flash cell, i.e. three bits as here with TLC. The pSLC cache also uses a significantly higher voltage for the one bit, which provides some security and is therefore better than Fast Page.

The use of pSLC cache offers a speed advantage, especially when the storage medium does not have read or write accesses between writing larger amounts of data. These idle times are used by the storage medium to move data from the cache to the TLC area.

But everyone knows the disadvantages of the pSLC. When the fast pSLC cache is full, the speed drops significantly because further write accesses to the storage medium must first free the pSLC by moving older data from the cache to the TLC memory.

But what is hidden behind “dynamic pSLC cache”? Dynamic pSLC cache has now also found its way into industrial storage solutions, but only with very hard restrictions. In contrast to the static pSLC cache, up to 100% of the NAND flash is used dynamically as pSLC cache, depending on how full the storage medium is. The cache can thus comprise up to 1/3 of the total memory size

However, the writing speed of the storage medium depends not only on the amount of data that is written without interruption, but also on the fill level of the memory. And this is exactly what makes the write speed in the life cycle difficult to predict.

NAND flash manufacturers do not recommend dynamically changing the configuration of flash blocks as pSLC or TLC memory for reliability reasons, but in the consumer sector, where the temperature windows are not so important, people are more relaxed about it.

All manufacturers of dynamic NAND storage media media, including Micron, permanently switch back to TLC mode after a specified maximum number of program and erase cycles. Before that, the storage medium achieves the best values especially in short write processes that do not require the entire capacity. However, the medium slows down permanently after a certain period of use, and you should never ignore that. Phison’s E18 handles dynamically changing the configuration of flash blocks quite well, but it can’t outsmart physics either.

When you will reach the end of the great cache performance is such a thing with imponderables here. After more than 250 GB in one piece, the glory was over for the time being and at a bit more than 80% of the capacity, you are only on a mediocre SATA level. In practice, this will hardly be possible, but it is better not to write in full in one piece and perhaps more than once.

6 Antworten

Kommentar

Lade neue Kommentare

Veteran

Neuling

Urgestein

Veteran

Mitglied

Neuling

Alle Kommentare lesen unter igor´sLAB Community →