Fürchterliche SoC-Spannungen überall! AMDs neuer Schrecken! Sagt YouTube. Aber um mehr über dieses Problem zu erfahren und um zu verstehen, warum auf den ersten Blick alles anders scheint, als es in Wahrheit nun einmal ist, müssen wir zur Quelle zurückkehren, die nichts anderes als SVI3 ist. In diesem Artikel werde ich heute versuchen, mehr Licht in diese Stromversorgungsschnittstelle zu bringen, die von den neuesten Prozessoren von AMD verwendet wird.

Nachdem ich den ersten Artikel und insbesondere das Video veröffentlicht hatte, beschwerten sich viele Benutzer, dass ich nicht hinter dem CPU-Sockel gemessen habe und dass es auf den PCB-Leiterbahnen einen erheblichen Spannungsabfall geben könnte. Da ich weiß, dass die entsprechenden Leiterbahnen dick genug sind, um KEINE hohen Spannungsabfälle zuzulassen, und aus der Tatsache, dass die VRMs Strommessleitungen haben, um ihre Ausgabe entsprechend der Last und den Spannungsabfällen anzupassen, war ich darüber nicht so besorgt. Trotzdem habe ich neue Messungen an den Messpads des Mainboards und hinter der CPU-Sockel durchgeführt.

Wie man sehen kann, beträgt der Abfall zwischen dem VRM-Ausgang des Mainboards und der Sockel nur 0,01445V, mit Prime95 laufend, das die CPU bis zum Maximum belastet. Da wir das jetzt auch geklärt haben, wollen wir mit dem Hauptartikel fortfahren, der sich auf SVI3 bezieht.

Das Scalable Voltage Interface 3 (SVI3)

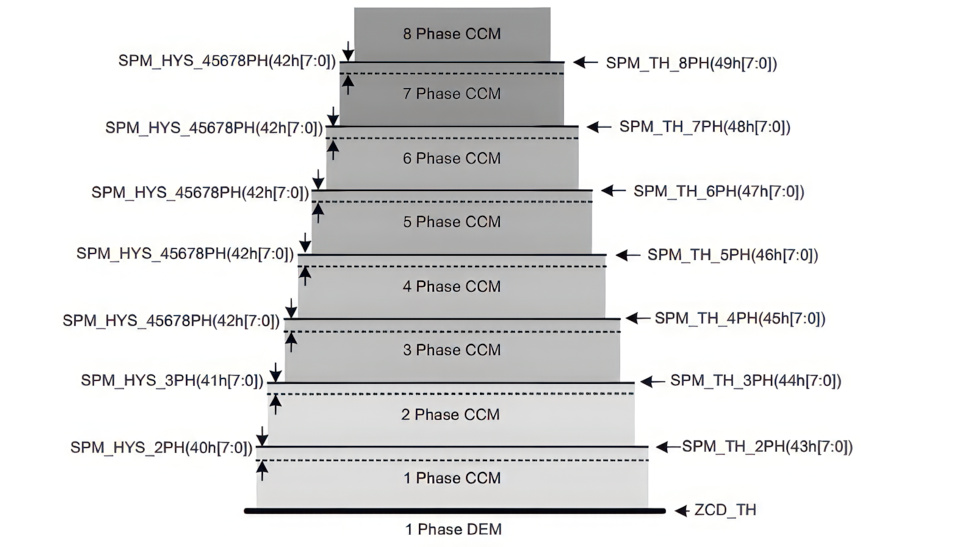

SVI3 ist so konzipiert, dass es eine schnellere und präzisere Kontrolle über die vom Prozessor benötigte Spannung ermöglicht. Es etabliert ein Zwei-Wege-Kommunikationsprotokoll zwischen der CPU und den Spannungsreglermodulen (VRMs) des Mainboards, wodurch die CPU ihre Stromanforderungen neben der Überwachung der Stromzufuhr steuern kann. Es gibt einige PWM-Controller, die mit der SVI3-Schnittstelle kompatibel sind. Die CPU hat Echtzeitinformationen über die Leistung und Betriebsbedingungen der VRM des Mainboards. Wenn die CPU nicht viel Strom benötigt, kann sie einige VRMs abschalten, um Energieverluste zu senken.

Die CPU kann die Leistungsphasen der VRMs aktivieren oder deaktivieren, indem sie den entsprechenden Befehl an den Leistungscontroller über den I2C-Bus sendet. Der AM5-Sockel hat drei verschiedene Stromschienen, über die die CPU mit Strom versorgt wird. Eine wird zwischen der CPU und den eingebetteten Grafikkernen geteilt; die SoC-Schiene dient hauptsächlich für den I/O-Die (IOD), und die VDD-Schiene ist für das Infinity Fabric und andere diverse Dinge.

Es gibt fast keine Informationen über SVI3 von AMD. Deshalb musste ich die ältere SVI2 suchen, auf der SVI3 basiert. Moderne CPUs müssen dynamisch überwachen und die Spannungsschienen, die sie speisen, entsprechend anpassen. Da die CPU die Last erzeugt, ist es ideal, ihre Stromquelle steuern zu können. Das könnte auch bei Netzteilen der Fall sein. Tatsächlich nutzen es die ATX v3.0 und PCIe 5.0 Standards durch den 12VHPWR-Anschluss und seine Sinussignale: CARD_PWR_STABLE und CARD_CBL_PRES# (Optional), die jedoch optional sind, und ich sehe sie letztendlich nicht implementiert.

Doch zurück zum eigentlichen Thema, die SVI2 und SVI3 sind Drei-Leitungs-Schnittstellen mit Takt (SVC), Daten (SVD) und Telemetrie (SVT) Leitungen. Die SVI2 und SVI3 Protokolle ähneln dem Konzept des I²C-Busses, so dass die CPU als Master Steuerpakete über die SVC (Takt) und SVD (Daten) Leitungen zu den VRM-Schaltungen des Mainboards sendet.

Bei SVI2 bestehen die Steuerpakete aus 3 Byte, die gemäß dem SMBus-Send-Byte-Protokoll übertragen werden: 1 Byte zur Auswahl des Spannungsbereichs (Kern oder SoC), gefolgt von einem Bestätigungsbit (ACK), und dann 2 Byte, die die anzuwendende Spannung und andere Konfigurationsparameter enthalten, jedes Byte gefolgt von einem ACK-Bit. Aufgrund der Konfigurationscodierung kann die Spannung mit einer Schrittgröße von 6,25 mV konfiguriert werden. Durch die Telemetriefunktions (TFN) Konfigurationsbits können periodische Spannungs- (und Strom) Berichte von der VR an die CPU über die SVC und SVT Leitungen aktiviert werden.

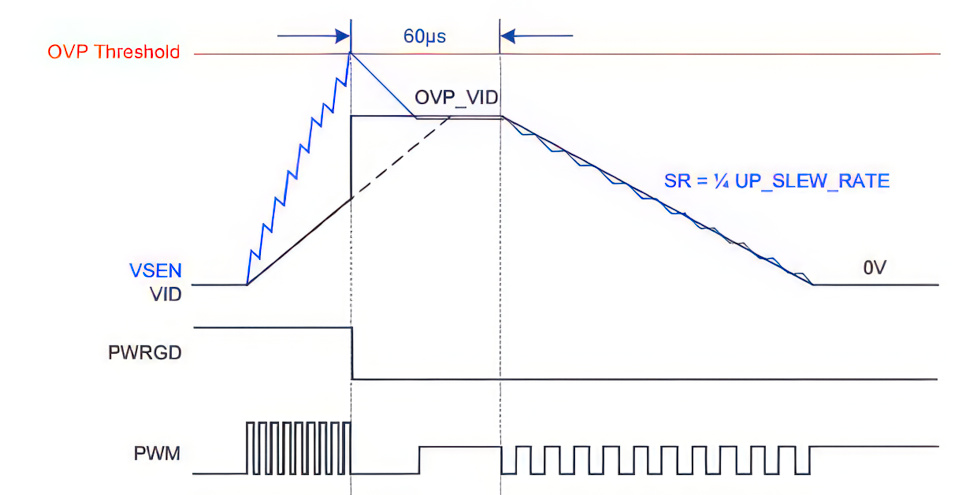

Bei SVI3 haben wir drei Schienen, Kern, SoC und VDD, daher muss im Steuerpaket das erste Byte für drei Optionen anstelle von zwei bei SVI2 verwendet werden. Die VRMs des Mainboards empfangen oder senden I2C-Signale über die I2C-Schnittstelle. Die CPU sendet verschiedene Befehle (Lesen/Schreiben/Zurücksetzen von Registern, VID/Adresspakete, Ändern des Stromzustands und Telemetrie-Anforderung) an die VRMs. Es gibt eine Loop-Steuerung, die die Ein-/Ausschaltsequenz der VRMs steuert, Schutzfunktionen handhabt und die PWM-Betrieb der VRMs steuert.

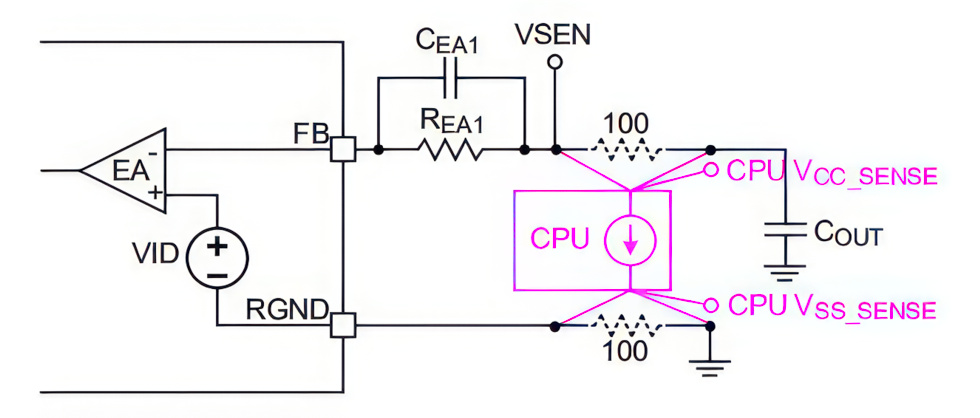

Die CPU enthält auf dem Die integrierte Sensoreingänge, VCC_SENSE und VSS_SENSE. Wenn keine CPU installiert ist und die Hersteller das Mainboard testen wollen, sind Paar von 100Ω Widerständen erforderlich, um den Stromkreis zu schließen und eine Spannungsrückmeldung zu liefern. VSEN und RGND müssen als differentielle Paare vom VRM-Controller zur CPU-Sockel verlegt werden, ohne irgendeinen Phasenknoten, Gate-Treiber, VIN-Stromlieferungspfad und Hochgeschwindigkeitssignale zu kreuzen. VSEN ist ideal für genaue Messungen, ohne Spannungsabfälle zu berücksichtigen.

Am wichtigsten ist, dass es eine Fernmessleitung zwischen den VRMs und der Last (der CPU) gibt, um die Spannungsabfälle entlang der PCB-Leiterbahnen, den internen Stromroutern der CPU und den Sockelnkontakten zu handhaben. Es gibt also nicht nur einen Spannungsabfall auf der Hauptplatine, sondern wir haben auch einen Abfall an den Stiften der Hauptplatine, die mit der CPU verbunden sind und innerhalb der CPU!

Für Telemetrieinformationen nimmt die CPU Daten vom Controller, der kontinuierlich die Ausgangsspannung der VRMs überwacht, vom differentiellen Spannungssensor-Eingang (VSEN-Pin und RGND-Pin). Einige Leistungsregler mitteln die Daten für eine höhere Genauigkeit, um Messrauschen zu reduzieren. Der Controller erfasst auch Informationen über den Stromausgang (Iout) und die Temperatur zur CPU. Wenn die CPU also feststellt, dass etwas nicht stimmt, kann sie durch die bereitgestellten Daten die entsprechenden Änderungen am VRM-Betrieb vornehmen.

Ich möchte feststellen, dass die meisten Schutzfunktionen vom Stromregler der Hauptplatine gehandhabt werden, einschließlich Überstrom-, Überhitzungs-, Unterspannungs- und Überspannungsschutz. Zum Beispiel, wenn der Überspannungsschutz ausgelöst wird, zwingt der Controller die Niederspannungs-MOSFETs einzuschalten, so dass die Hochspannungs-MOSFETs ausgeschaltet werden und die VRMs von der Eingabe des Netzteils (12V) getrennt werden.

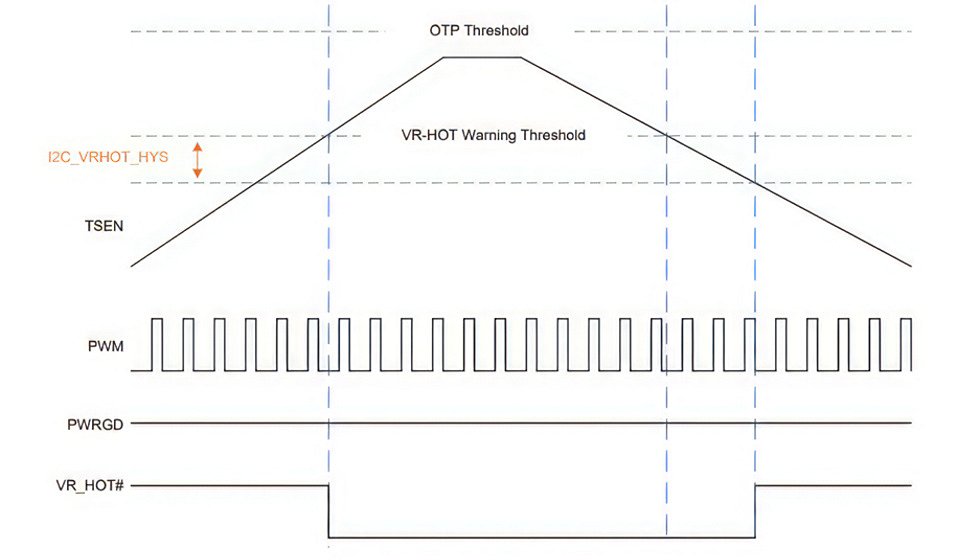

Bezüglich des Überhitzungsschutzes, wenn der Controller ein “Überhitzung”-Signal erhält, übermittelt er es an die CPU über den I2C-Bus, und es reduziert den Stromverbrauch durch Reduzierung der CPU-Last. Deshalb ist die Qualität der VRMs für die Geschwindigkeit der CPU wichtig. Wenn VRMs während einer Überlastung schnell heiß werden, muss die CPU ihre Last reduzieren, um sie abkühlen zu lassen.

Schlussfolgerungen und Fazit

Aus alldem können wir zu den folgenden Schlussfolgerungen kommen:

- SVI3 ermöglicht es der CPU, die VRM-Phasen des Mainboards vollständig zu steuern.

- SVI3 kann nicht nur Messungen durchführen, sondern auch alle Arten von Messungen bereitstellen, einschließlich natürlich aller Spannungspegel, die den entsprechenden Schaltkreisen der CPU zugeführt werden.

- Die einzige Möglichkeit, Spannungsmessungen innerhalb der CPU zu erhalten, besteht darin, SVI3 zu nutzen.

- Wir können nicht wissen, ob die Messungen, die SVI3 innerhalb der CPU liefert, genau sind, da wir sie nicht extern messen können.

- Es gibt einen Spannungsabfall zwischen dem VRM-Ausgang des Mainboards und dem Sockel, der in meinem Fall, für den VSOC, unter Vollast, 0.01445V beträgt.

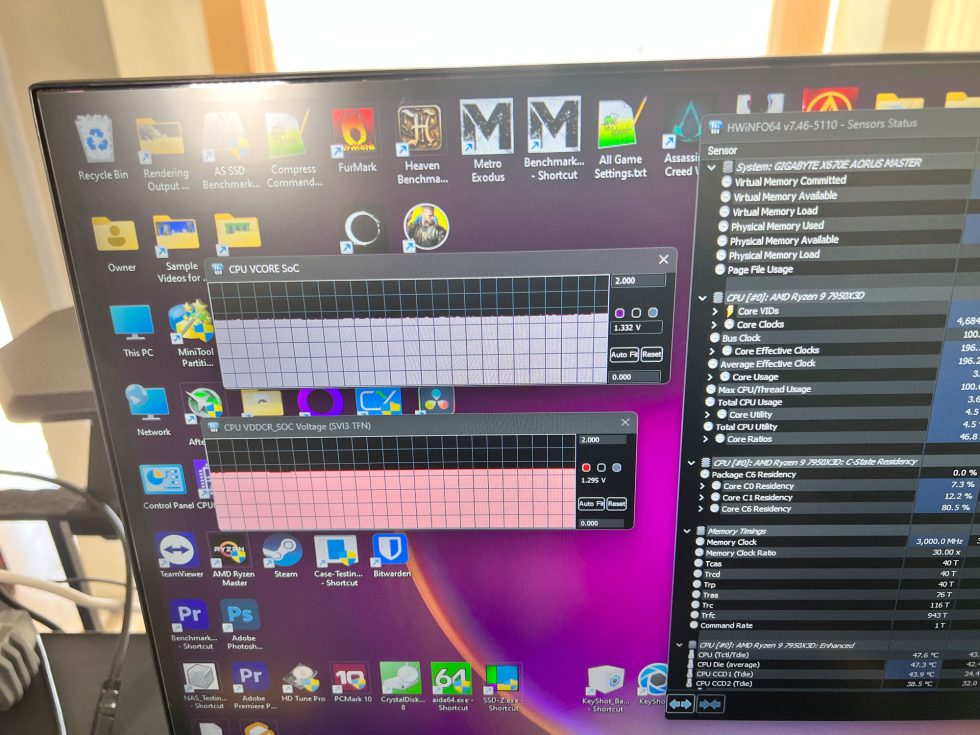

- Es gibt einen Spannungsabfall zwischen dem Stromanschluss des Sockels und dem, was die internen Schaltkreise der CPU erhalten, aufgrund der Verbindungen durch die Stifte des Mainboards und der Stromverluste innerhalb der internen Stromleitungen der CPU. In meinem Fall habe ich 1.35294V auf der Rückseite des Sockels gemessen, während die CPU VDDCR_SOC (SVI3 TFN) Spannung, wie von HWinfo gemeldet, 1.295V betrug. Das bedeutet, dass von der Rückseite des Sockels bis zum entsprechenden Schaltkreis der CPU der Spannungsabfall 0.05794V beträgt, während, wenn man den VRM-Ausgang der Hauptplatine als Ausgangspunkt nimmt, der Spannungsabfall 0.07239V beträgt, was erheblich ist.

AMD hat erklärt, dass alles über 1.30V VSOC unsicher ist und vermieden werden sollte, hat aber nicht klargestellt, an welchem Punkt. An den VRMs des Mainboards, an der Rückseite der Sockel oder im internen Schaltkreis der CPU? Ich habe mich mit Leuten von Gigabyte unterhalten und sie haben mir gesagt, dass sie versuchen, die VSOC-Spannung laut den Informationen von SVI3 unter 1.3V zu halten, was bedeutet, im Inneren der CPU, wo wir keine Messungen durch physische Mittel machen können, sondern nur durch Software. Eine niedrigere VSOC SVI3 Spannung als 1.30V, zum Beispiel 1.25V, schafft Probleme für RAM-Kits mit aktiviertem EXPO-Profil.

Aus alledem kann ich sicher annehmen, dass, wenn man seine Hauptplatine CPU VDDCR_SOC Spannung (SVI3 TFN) überprüft und feststellt, dass sie unter 1.30V liegt (während ein stressiger Benchmark läuft und EXPO aktiviert ist), man auch sicher sein kann, dass alles immer gemäß AMDs Vorgaben läuft. Für mich ist es ein Problem, dass ich keine physischen Messungen dieser Spannung vornehmen kann und ich bin durch den erheblichen Spannungsabfall von 0.05794V zwischen der CPU-Sockel und dem Schaltkreis innerhalb der CPU beunruhigt. Aber dieser soll bei Intel sogar noch höher sein.

Referenzen und Quellen:

- Advanced Micro Devices, Inc. 2018. Understanding Power Management and Processor Performance Determinism. Retrieved 2023-05-17 from https://www.amd.com/system/files/documents/understanding-power-management.pdf

- Buhren, R., Jacob, H. N., Krachenfels, T., & Seifert, J. (2021). One Glitch to Rule Them All: Fault Injection Attacks Against AMD’s Secure Encrypted Virtualization. ArXiv. /abs/2108.04575

- Renesas Electronics Corporation. 2020. ISL62776 Multiphase PWM Regulator for AMD CPUs Using SVI2. Retrieved 2023-05-17 from https://www.renesas.com/us/en/document/dst/isl62776-datasheet

- Richtek Technology Corporation. 2023. Dual Channel PWM Controller with I2C Interface Control for AMD SVI3 CPU/GPU Core Power Supply. Retrieved 2023-05-17 from https://www.richtek.com/assets/product_file/RT3667BT/DS3667BT-00.pdf

Mein Dank geht an den Gastautor, dessen Erkenntnisse ich natürlich gern teile. Wer mehr zu Aris, hwbusters.com (hier erschien auch dieser Artikel als Erstveröffentlichung) und Cybenetics erfahren möchte, dem seien die jweiligen Homepages ans Herz gelegt. Man findet dort einzigartigen Content, der auf echten und unabhängigen Messungen basiert. Ich empfehle auch den neuen Powenetics V2 PMD bzw. die Lektüre zum Produkt:

164 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Mitglied

Urgestein

1

Urgestein

Veteran

Veteran

1

1

Urgestein

Urgestein

1

Mitglied

1

Urgestein

Urgestein

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →