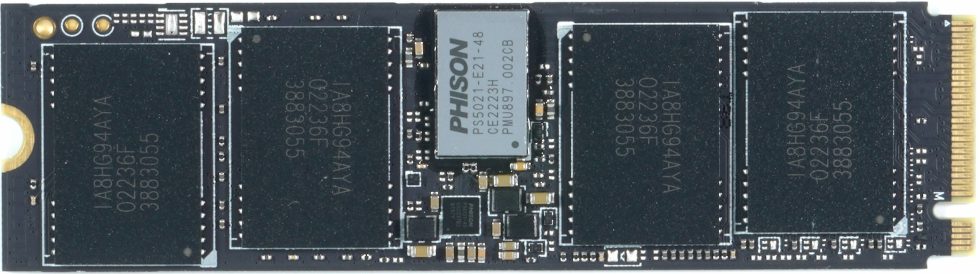

Ich hatte es ja bereits geschrieben, dass man die Sticker für eine gute Performance besser abnehmen sollte, denn die 4 bis reichlich 5 Watt Peak (gemessen) bei maximaler Auslastung wollen ja auch beidseitig gut abgeführt werden. Hat man das erledigt, liegt der Blick auf die Platine frei, die wieder von TECHVEST kommt, jedoch auf Corsair individualisiert und auch von Corsair bestückt wurde. Die MP600 GS nutzt im Gegensatz zu den schnelleren Modellen nicht mehr den Phison E18, sondern sie setzt bewusst auf den kleineren und sparsameren Phison E21T.

Dieser besitzt nur einen Kern (ok, es sind insgesamt drei zusammen mit dem Co-Prozessor) und mit vier NAND-Channels auch nur die Hälfte der Pro XT. Außerdem muss die SSD auf einen dedizierten DRAM-Cache verzichten und greift stattdessen via Host-Memory-Buffer (ab Windows 10) auf den normalen System-RAM des Rechners zu. Kann man durchaus machen, denn im Normalfalls reicht selbst dieses standardmäßige NVMe-Feature, um das Fehlen eines eigenen DRAM-Caches auszugleichen.

Der Controller kommuniziert mit dem NAND über vier NAND-Flash-Kanäle mit bis zu 1.600 MTps und unterstützt Kapazitäten von bis zu 4 TB mit 16 Chips. Unser Muster enthält einseitig vier Module (Micron B47R, 8 Dies zu je 512 Gigabit), die dank der geringen Größe des Controllers locker Platz finden. Das Design nutzt, wie bereits erwähnt, jedoch keine DRAM-basierte Architektur mehr. Es wäre auch kein Platz mehr gewesen. Im getesteten 2-TB-Modell befinden sich somit 32 dieser 512-GB-Flash-Chips in Form von Microns neuem 176-Layer-NAND (B47R), die im vorliegenden Modell alle mit der gleichen Geschwindigkeit von 1.200 MTps arbeiten.

Bei den verbauten Chips handelt es sich um eine Quad-Plane-Replacement-Gate-Architektur, die metallbasierte Control Gates sowie einige andere Design- und Produktionsoptimierungen zur Steigerung der Leistung und Ausdauer verwendet. MSI nutzt bei der SPATIUM M480 noch Microns 96-Layer B27B. Was übrigens passiert, wenn man den Sticker im kalten Zustand entfernt, zeigt das nächste Bild:

Der Phison E21T erfüllt die NVMe 1.4-Spezifikation und verfügt über eine Reihe von üblichen Funktionen. So unterstützt er sowohl Trim- als auch S.M.A.R.T.. Wie andere Controller auch, nutzt er Active State Power Management (ASPM), Autonomous Power State Transition (APST) und den L1.2 Ultra-Low-Power-Status (siehe Datenblatt Seite 1). Eine thermische Drosselung ist implementiert, ist aber nicht weiter von Belang, da der Controller in den meisten Anwendungsfällen nicht zu heiß wird. Das erkennt man auch daran, dass man im Gegensatz zu den älteren Modellen wie dem E16 auf einen integrierten Nickel-Kühlkörper verzichten kann.

Außerdem nutzt er die LDPC ECC-Engine der vierten Generation, SmartECC (RAID ECC) und eine End-to-End Data Path Protection für eine robuste Fehlerkorrektur und verbesserte Datenzuverlässigkeit. Er unterstützt sogar hardwarebeschleunigte AES 128/256-Bit-Verschlüsselung (die TCG-, Opal 2.0- und Pyrite-konform ist) und verfügt über eine integrierte Krypto-Löschfunktion. Der E12T von Phison unterstützt wie die Modelle E12S und E16 ein volldynamisches Schreibcaching. Die Größe des dynamischen pSLC-Caches, auf den ich gleich noch eingehen werde, beträgt daher maximal 1/3 der verfügbaren Kapazität des TLC-Laufwerks. Phison hat außerdem SmartFlush implementiert, was eine schnelle Wiederherstellung des Cache für eine vorhersehbare und konstante Leistung ermöglicht. Soweit die Theorie. Naja, nicht ganz.

Was bedeutet eigentlich dynamischer pSLC Cache?

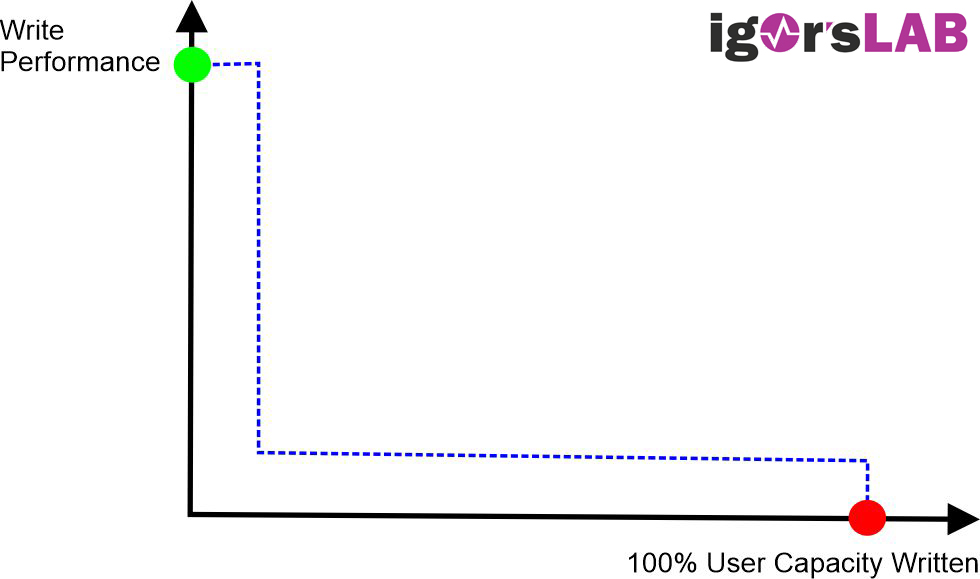

Kommen wir nun zu einem etwas technischeren Detail, das den meisten so gar nicht im vollen Umfang bekannt sein dürfte. Über pSLC-Cache ist ja schon viel geschrieben worden, das muss man gar nicht noch einmal im Detail durchkauen, maximal noch als kleine Auffrischung. Here we go…

Um die Schreibgeschwindigkeit zu erhöhen, wird gern der sogenannte „Pseudo-SLC Cache“ (pSLC) in Consumer-Produkten genutzt, wobei man ihn mittlerweile auch in diversen industriellen Lösungen findet. Hierfür wird ein Teil der NAND-Kapazität als SLC-Speicher konfiguriert, in dem nur ein Bit pro Zelle gespeichert wird. Dementsprechend kann dieser Speicher sehr schnell beschrieben und gelesen werden. Da es sich nicht um dedizierten, also keinen echten SLC-Speicher handelt, wird er pseudo SLC genannt. Ein solcher Cache kann für alle Speichertypen verwendet werden, die mehrere Bits pro Flash-Zelle speichern, also wie hier beim TLC drei Bits. Der pSLC Cache nutzt bei dem einen Bit zudem eine deutlich höhere Spannung, was eine gewisse Sicherheit bietet und damit besser ist als Fast Page.

Die Verwendung von pSLC-Cache bietet einen Geschwindigkeitsvorteil, vor allem dann, wenn das Speichermedium nicht mit Lese- oder Schreibzugriffen zwischen dem dem Schreiben größerer Datenmengen. Diese Leerlaufzeiten werden vom Speichermedium genutzt, um Daten aus dem Cache in den TLC-Bereich zu verschieben.

Doch die Nachteile des pSLC kennt jeder. Wenn der schnelle pSLC-Cache nämlich voll ist, sinkt die Geschwindigkeit deutlich ab, da weitere Schreibzugriffe auf das auf das Speichermedium erst den pSLC freimachen müssen, indem man ältere Daten aus dem Cache in den TLC Speicher verschiebt.

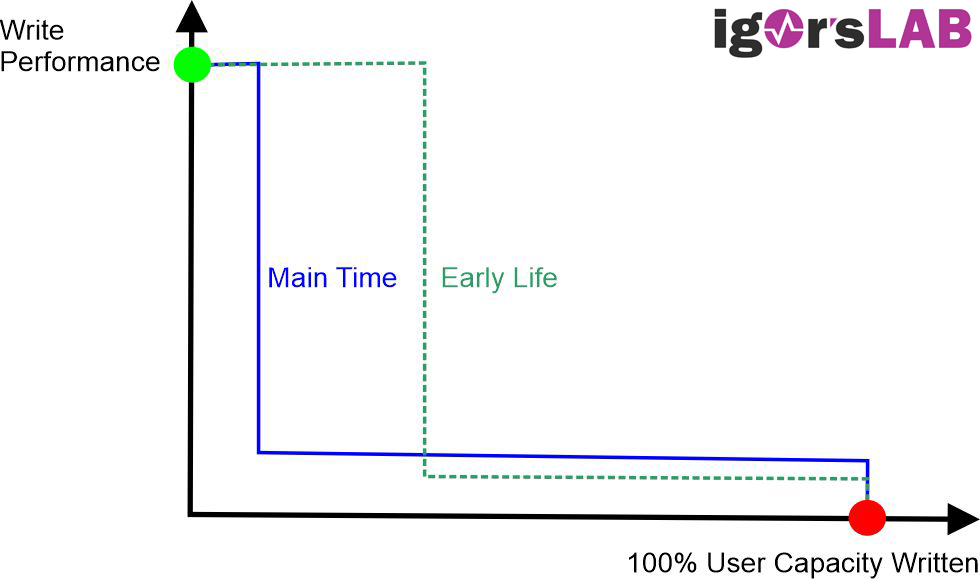

Doch was bitte versteckt sich jetzt hinter „dynamischem pSLC Cache“? Dynamischer pSLC-Cache hat zwar mittlerweile auch seinen Weg in industriellen Speicherlösungen gefunden, aber nur mit sehr harten Einschränkungen. Im Gegensatz zum statischen pSLC-Cache werden bis zu 100 % des NAND-Flash dynamisch als pSLC-Cache genutzt, je nachdem, wie voll das Speichermedium ist. Der Cache kann also bis zu 1/3 der Gesamtspeichergröße umfassen

Die Schreibgeschwindigkeit des Speichermediums hängt allerdings nicht nur von der Datenmenge ab, die ohne Unterbrechung geschrieben wird, sondern auch vom Füllstand des Speichers. Und genau das macht die Schreibgeschwindigkeit im Lebenszyklus nur schwer vorhersagbar.

Von einer dynamischen Änderung der Konfiguration von Flash-Blöcken als pSLC- oder TLC-Speicher wird von den NAND-Flash-Herstellern aus Gründen der Zuverlässigkeit zwar abgeraten, aber im Consumer-Bereich, wo die Temperaturfenster nicht so sehr von Belang sind, sieht man das durchaus etwas entspannter.

Alle Hersteller von dynamischen NAND-Speichermedien Medien, auch Micron, wechseln nach einer festgelegten Maximalanzahl von Programm- und Löschzyklen dauerhaft in den TLC-Modus zurück. Davor erreicht das Speichermedium die besten Werte vor allem bei kurzen Schreibvorgängen, die nicht die gesamte Kapazität benötigen. Nach einer gewissen Nutzungszeit wird das Medium jedoch dauerhaft verlangsamt, das darf man nie ausblenden. Der E18 von Phison beherrscht die dynamische Änderung der Konfiguration von Flash-Blöcken recht gut, aber die Physik überlisten kann er auch nicht.

Wann man dann das Ende der tollen Cache-Performance erreichen wird, ist hier so ein Ding mit Unwägbarkeiten. Nach reichlich 250 GB im Stück war erst einmal Schluss mit der Herrlichkeit und bei etwas mehr als 80% der Kapazität liegt man nur noch auch mittelmäßigem SATA-Niveau. Das wird man in der Praxis so zwar kaum hinbekommen, aber im Stück vollzuschreiben und das vielleicht auch öfters, sollte man besser lassen.

6 Antworten

Kommentar

Lade neue Kommentare

Veteran

Neuling

Urgestein

Veteran

Mitglied

Neuling

Alle Kommentare lesen unter igor´sLAB Community →