In a new rumor from Greymon55, it looks like AMD’s RDNA 3 based Navi 33 GPU planned for the upcoming Radeon RX 7000 series graphics cards will have fewer cores than initially expected. Previously Greymon55 had stated up to 5120 cores or 20 WGP’s on the RDNA 3 based Navi 33 GPU, but his latest information indicates a lower WGP and core count. However, this doesn’t mean that the overall performance has changed. Despite the lower number, the Navi 33 GPU should offer faster GPU performance than the current Navi 21 GPU, which is currently AMD’s flagship RDNA 2 chip for the high-end segment.

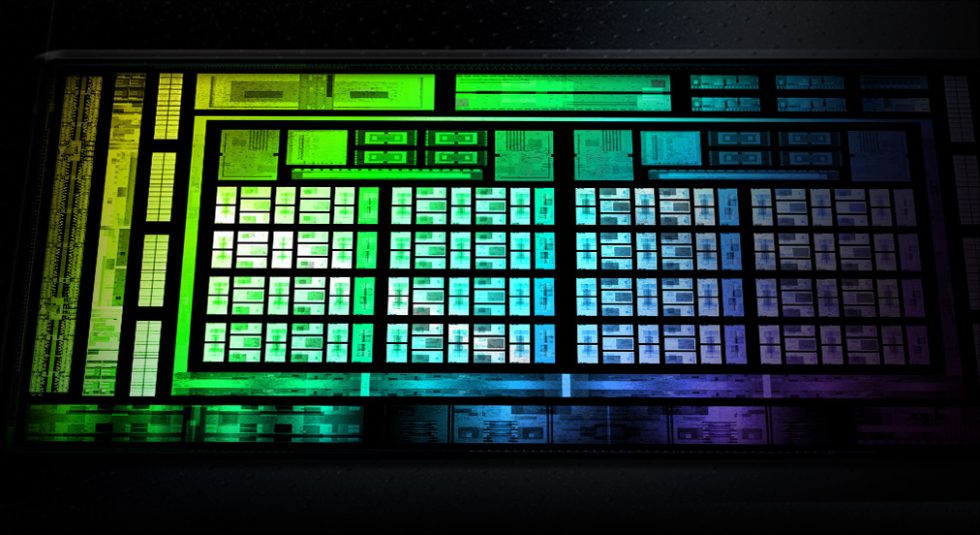

The AMD Navi 33 GPU will open up the monolithic segment within the RDNA 3 family, so de facto covering everything from mid-range down, for the upper-range and high-end you’d expect an MCM design (which I had already announced over two years ago). This base GPU will consist of a single chip that can be used to scale up later in the MCM design. The die is very similar to the flagship Navi 21 GPU and is expected to be manufactured in TSMC’s 6nm node.

Another and bigger Navi chip? First indications of a possible multi-chip package!

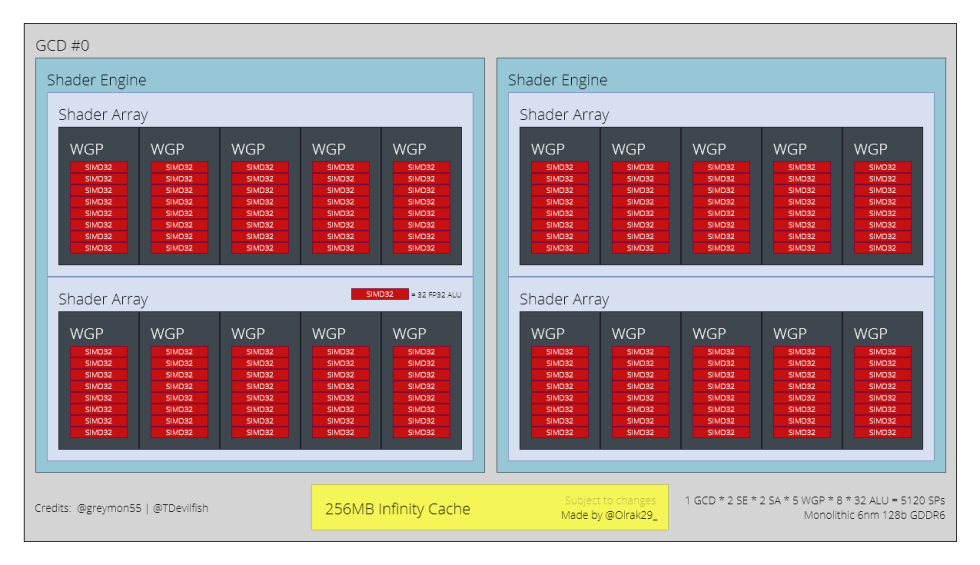

The Navi 33 GCD is expected to have 2 shader engines and each of these shader engines would then have 2 shader arrays (2 per SE / 4 total). Each shader array previously consisted of 5 WGPs (10 per SE / 20 total) and each WGP has 8 SIMD32 units with 32 ALUs (40 SIMD32 per SA / 80 per SE / 160 total). These SIMD32 units add up to 5120 cores, which is the same core count as the RX 6900 XT (Navi 21 XTX GPU).

However, based on the new numbers, the RDNA 3 Navi 33 GPU will have a total of 16 WGPs or 4096 cores. It’s not known if this is the specific configuration of the chip itself that has been updated here, or if the new Radeon RX 7000 cards feature a reduced Navi 33 chip configuration with WGP disabled in each shader array.

>n33 6nm 128bit gddr6 perf>6900xt

Doubt

— Meta (@Meta42236970) September 21, 2021

Kopite7kimi stated in a subsequent tweet that Navi 33 is the replacement for Navi 23 on the GFX11 architecture, but we do know that Navi 23 only has 2048 cores, half the amount that is supposedly in Navi 33. The Navi 23 GPU is currently used in the Radeon RX 6600 series cards, so it’s safe to assume that Navi 33 could probably be meant for the RX 7600 series, unless AMD wants to move its lineup up a notch and use Navi 31 for the RX 7900 series, Navi 32 for the RX 7800 series, and Navi 33 for the RX 7700 series. The RX 7600 range and below could then be based on the refreshed RDNA 2 GPUs in 6nm.

Am I the only one who noticed @greymon55's new bio?

Navi33 is apparently 4096SPs, not 5120

That means an RDNA3 card that can (presumably) beat Navi21 is just 16WGPs

Of course, this begs the question of where the 60WGP Navi31 would land

/1 pic.twitter.com/kqQDHfURIw— WildCracks (@wild_cracks) September 28, 2021

Navi 33 (RDNA 3) is expected to come with 256 MB of Infinity Cache. Each GPU should also have 2 memory connect links (32-bit). That’s a total of four 32-bit memory controllers for a 128-bit bus interface. This would certainly catapult the AMD Radeon RX 7600 series performance over the RX 6800 and RX 6900 series at a TDP of around 200W, especially at higher resolutions. The market launch could take place in autumn 2022.

Source: Greymon55/Kopite7kimi via WCCFTECH

3 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Mitglied

Veteran

Alle Kommentare lesen unter igor´sLAB Community →