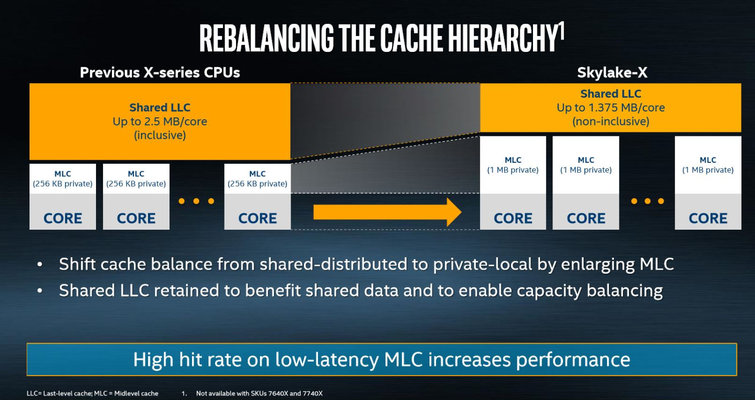

Intel has reduced the shared Last Level Cache (LLC-L3) and transferred it from an inclusive to a non-inclusive (but exclusive) approach. This was done with the help of an efficient caching algorithm that maximizes the hit rate of the L2 cache. This reduces the L3 cache per core to 1.375 MB, making it a kind of residual cache that captures the data that is thrown out of the private L2 cache.

Intel has also increased the per-core Mid Level Cache (MLC-L2) from 256 KB to 1 MB, benefiting from multi-threaded performance. Unfortunately, Intel has not provided any information on how these changes to its Skylake core design were technically implemented in The.

Cache & Memory Latency and Bandwidth

IPC, AVX, Encryptions

Due to the limited time until the Skylake X launch, we used a preliminary set of benchmarks to compare IPC performance. We've also worked with various BIOS updates, so it's quite possible that future optimizations or a more complex set of workloads can reveal completely different averages than current ones. For all subsequent tests we have chosen a static clock frequency of 3.0 GHz. It is also important to note that Intel does not explicitly provide us with the source of improvements to the IPCs of 15 and 15. 10 percent for single-threaded or multi-threaded workloads. Instead, Intel relies on the Spec*int_rate_base2006 benchmark, which has a fairly high error rate of +/- 5 percent.

The single-threaded Cinebench test run shows no big differences in performance average between the Skylake-X Core i9-7900K, the Kaby Lake i7-7700K and the Skylake Core i7-6700K. Slight improvements of 5.69 percent compared to the Broadwell-E i7-6950X. With the switch to the multi-thread test run of the Cinebench, the differences between the ten-core processors and the rest become greater and the focus is now on the i7-7900X and the i7-6950X, where we were able to determine a delta of 1.93 percent.

The Core i9-7900X has two 256-bit-wide AVX FMA units per core that work in parallel, while AMD splits 256-bit AVX operations into two FMA units per core. Intel disables one FMA unit per core on the Skylake X models with fewer than ten cores. Thus, the i9-7900X has a system-immanent advantage in the y-cruncher benchmark, which is both a single and a multi-threaded program that calculates the number Pi with AVX instructions. In fairness, we used version 0.7.2.9469, which already comes with a Ryzen optimization.

The test results of the i9-7900X, when only one core is used, are nearly twice as high as those of the previous model, which is probably mainly due to Intel's AVX2 optimization. The advantage is equally evident in the multi-thread test. Intel provides AVX-512 support for Skylake processors, but does not implement all of the 11 features into the desktop chips. Instead, selected opportunities are offered in specific market segments.

The Zen architecture relies on two AES modules to accelerate encryption, so it's little wonder that the Ryzen chips dominate the AES-256-ECB single-core test run. Intel processors, on the other hand, play their advantage of the larger number of CPU cores in threaded AES workloads.

- 1 - Einführung und Übersicht

- 2 - Intels Fabric - Mesh statt Ringbus

- 3 - Cache und Latenzen, IPC, AVX und Kryptographie

- 4 - Chipsatz, Testsystem und -methoden

- 5 - Problemanalyse mit Civilization VI und VRMark

- 6 - AotS Escalation, Battlefield 1, Deus Ex: Mankind

- 7 - GTA V, Hitman, Shadow of Mordor

- 8 - Project Cars, Rise of the Tomb Raider, The Division

- 9 - Workstation und HPC

- 10 - Leistungsaufnahme und Übertaktung

- 11 - Temperaturverläufe und thermische Probleme

- 12 - Zusammenfassung und Fazit

Kommentieren