tRTP / tRDPRE erklärt

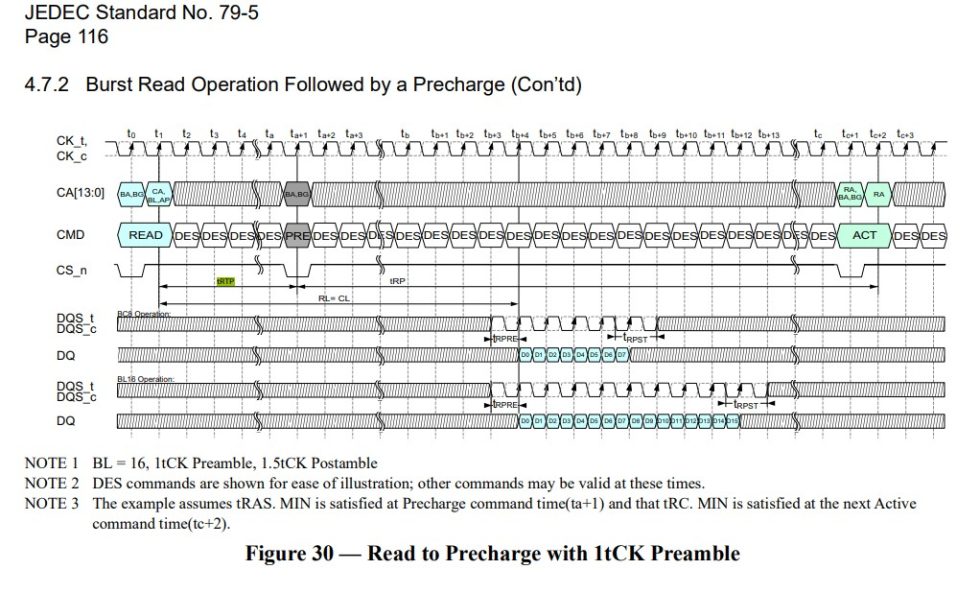

Das Timing tRTP wie es von JEDEC genannt wird, gibt es so tatsächlich bei Intel Speichercontrollern gar nicht. Stattdessen gibt es das tRDPRE Timing, das effektiv aber nur eine andere Abkürzung für die Beschreibung der selbe Funktion ist. Nach einem Lesevorgang muss eine Reihe und die zugehörige Bank und Bank Group nämlich wieder deaktiviert und dabei geladen werden, damit sie später wieder aktiviert und gelesen werden kann. Dieser Vorgang heißt Precharge und wird vom Timing tRP gesteuert. tRTP bzw. tRDPRE definiert nun, wie viel Zeit zwischen dem Ende des Lesevorgangs und dem Deaktivieren und Laden vergeht. Auch hier ähnelt das Prinzip wieder einer „Verschnaufpause“ nach dem Lesevorgang, ehe die Bank Group wieder in den Ausgangszustand versetzt wird.

tRTP wird im offiziellen JEDEC Dokument für DDR5 so definiert, dass der minimale unterstützte Wert das Maximum aus 12nCK (Anzahl Taktzyklen) oder 7,5 ns ist. Hierfür ist dann natürlich die Taktrate relevant, um bestimmen zu können, ob 12 Taktzyklen länger sind als 7,5 ns. Für DDR5-4800 ist die tatsächliche Taktrate bekanntlich 2400 MHz – DDR = Double Data Rate. 1 nCK entspricht damit also 1 s / 2400000000 oder auch 4,16 e ^ -10 s. 12 Stück davon sind entsprechend 5 e^-9 s oder 5 ns. Das Maximum aus 12 nCK und 7,5 ns sind also bei DDR5-4800 7,5 ns.

Anders herum lässt sich dies auch wieder zurück in Taktzyklen umrechnen, um den minimalen Timing-Wert zu ermitteln, der gemäß JEDEC supportet ist. Hierfür teilen wir einfach die 7,5 ns durch die Dauer eines einzelnen Taktzyklus und runden dies auf die nächste Ganzzahl. 7,5 e^-9 s / 4,16 e^-10 s = 18,02. Somit liegt der niedrigste, gemäß JEDEC unterstützte Wert für tRTP bei DDR5-4800 eigentlich bei 19 und nicht bei 12.

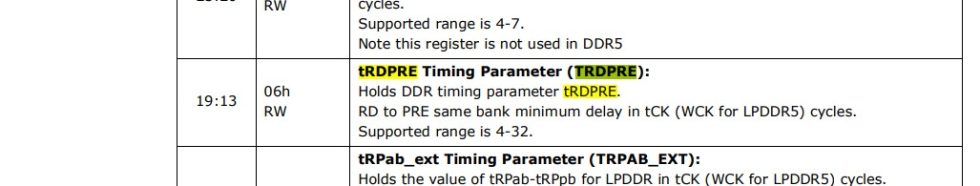

Was sagt nun Intel dazu? Nichts, denn genau genommen spezifiziert Intel das Timing überhaupt nicht. Stattdessen übernimmt das andere Timing tRDPRE effektiv diese Funktion. Entsprechend kann man auch bei den meisten Mainboards im BIOS tRTP auf Auto belassen und den Wert stattdessen via tRDPRE steuern, womit teilweise niedrigere Werte möglich sind, aber das nur am Rande. Intel spezifiziert in ihrer Dokumentation gar keine effektiven Zeiträume, sondern lediglich eine Anzahl an Taktzyklen. Im Fall von tRDPRE ist der unterstützte Bereich 4 – 32.

Wenn wir dies zur Referenz wieder in Nanosekunden für DDR4-4800 umrechnen, landen wir bei 1,67 ns bzw. 13,312 ns und damit mit dem Minimum deutlich unter dem JEDEC Standard. Ein Maximum gibt JEDEC übrigens gar nicht an. Um das nochmal für DDR5-4800 zusammenzufassen: Intel spezifiziert ein Minimum von 1,67 ns, während JEDEC ein Minimum von 7,5 ns definiert. Das ist ein krasser Unterschied, der mit steigenden Taktraten nur noch größer wird, da der JEDEC Wert fix ist, der Intel Wert aber invers proportional mit der Taktrate schrumpft. Aber was bringt nun die meiste Performance? Auch das haben wir mit mehreren Abstufungen für den Timing Wert ertestet.

8 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Veteran

Mitglied

Urgestein

Urgestein

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →