Activates (tRRD_S, tRRD_L, tFAW) erklärt

Zunächst haben mich die 3 „Activate Timings“ interessiert, die aufgrund ihrer Abhängigkeiten zueinander immer zusammen betrachtet werden sollten. Aber was ist ein „Activate“? Um das zu verstehen, muss man eigentlich nur wissen, dass die Speicherzellen von RAM in Reihen und Bänken organisiert sind und diese wiederum in Gruppen zusammengefasst werden – Bank Groups. Wer unseren DDR5 Deep Dive Artikel gelesen hat, wird sich vermutlich daran erinnern, dass DDR5 8 statt 4 Bank Groups hat, aber das nur am Rande.

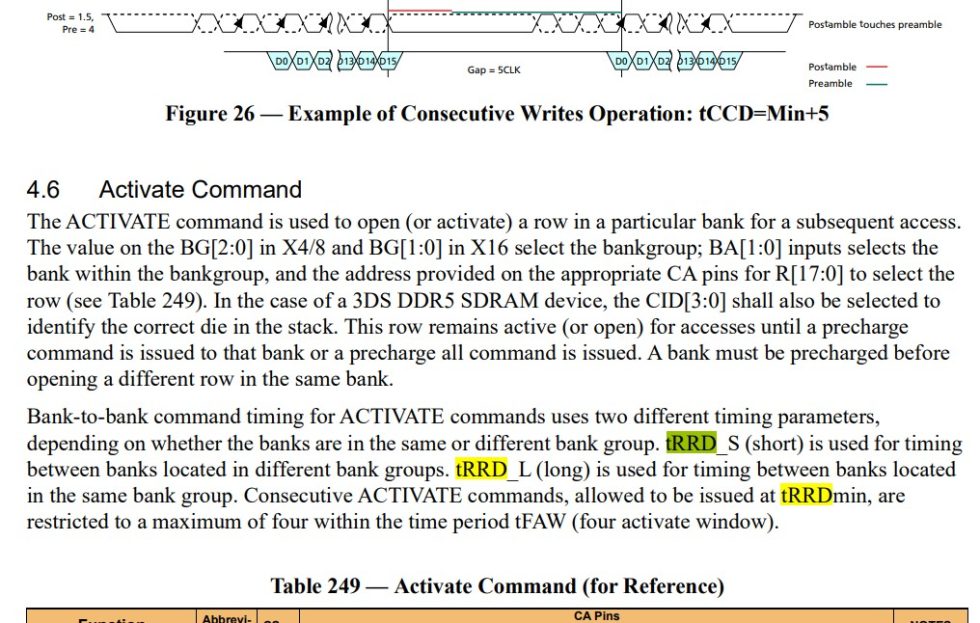

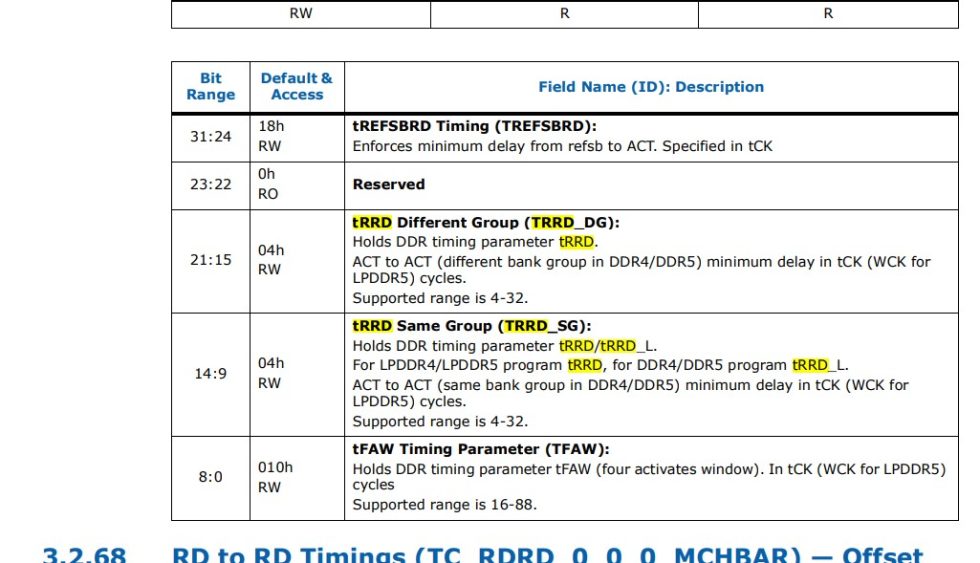

Wenn nun auf eine Speicheradresse in einer Bank zugegriffen werden soll, muss deren Bank Group aktiviert werden. Und die Activate Timings definieren, wie schnell hintereinander diese Aktivierungen stattfinden können. Dabei wird unterschieden, ob es sich um die selbe Bank Group handelt wie zuvor oder eine andere. Ersteres dauert gewöhnlich länger, da sich die Bank Group noch vom vorherigen Aktivieren „erholen“ muss, womit sich die Benennung des Timings erklärt, tRRD_L (long) bzw. tRRD_sg (same group). Entsprechend bedeutet tRRD_S (short) bzw. tRRD_dg (different group), dass eine Bank in einer anderen Bank Group als zuvor aktiviert werden soll, was meist schneller geht.

Nun ist nur noch wichtig, dass immer 4 Activates hintereinander ausgeführt werden können. Das Four Activate Window (tFAW) beschreibt wie lange das Zeitfenster für 4 Activates mindestens geöffnet bleibt. Sinnvoll dimensioniert wird dieses Timing also mit mindestens 4 * Min (tRRD_S, tRRD_L). Wenn 4 Activates länger dauern würden als tFAW, bleibt das Fenster dennoch geöffnet und tFAW wird effektiv erweitert. Das Timing beschreibt also lediglich eine Minimaldauer, womit man den RAM Bank Groups nach 4 Activates noch eine „Verschnaufpause“ einrichten kann. Bei den meisten modernen RAM ICs ist dies aber nicht nötig und die Formel tFAW = 4* Min (tRRD_S, tRRD_L) für die Bemessung völlig ausreichend.

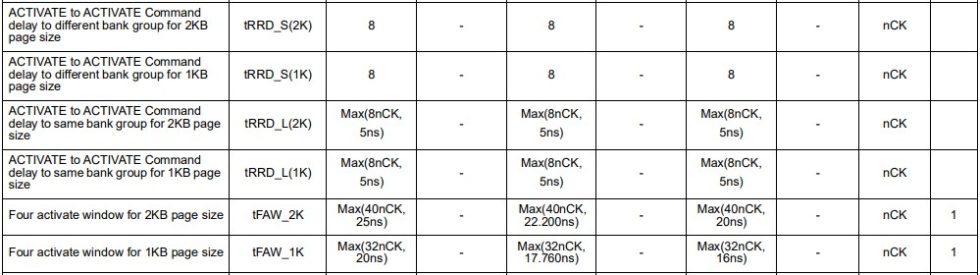

tRRD_S wird im JEDEC Dokument für DDR5 so definiert, dass dieses mindestens 8 nCK, also 8 Taktzyklen lang ist. Somit lässt sich die tatsächliche Dauer relativ simpel wie folgt berechnen: Für DDR5-4800 ist die tatsächliche Taktrate bekanntlich 2400 MHz – DDR = Double Data Rate. 1 nCK entspricht damit also 1 s / 2400000000 oder auch 4,16 e ^ -10 s. 8 Stück davon sind entsprechend 3,328 e^-9 s oder 3,328 ns. Diese Rechenübung ist hier noch eher akademischer Natur, wird aber beim nächsten Timing schon deutlich wichtiger.

tRRD_L wird als Minimalwert nämlich als 8 nCK (Anzahl Taktzyklen) oder 5 ns definiert, was auch immer davon größer ist. Von eben wissen wir bereits, dass 8 nCK bei DDR5-4800 3,328 ns sind. Somit greift der größere statische Wert von 5 ns als effektives Minimum laut Spezifikation. Damit wir nun wissen, welchen Wert wir beim Timing einstellen müssten, um diesem Minimum zu entsprechen, lässt dich die Rechnung einfach umkehren. 5 ns / 0,416 ns (1 nCK bei DDR5-4800) = 12,02. Da sich natürlich nur Ganzzahlen bei den Timings einstellen lassen, wäre das Minimum für tRRD_L bei DDR5-4800 laut JEDEC 13.

Intel befasst sich im Gegenteil gar nicht mit effektiven Zeitspannen, sondern spezifiziert lediglich Anzahl von Taktzyklen für die Timings, und zwar jeweils 4 für tRRD_S und tRRD_L und folglich 16 für tFAW. Welche Konfiguration bringt denn jetzt aber bei DDR5 die meiste Performance, JEDEC mit 8/13/32, Intel mit 4/4/16 oder doch eine ganz andere Kombination? Die Tests auf der nächsten Seite verraten es.

8 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Veteran

Mitglied

Urgestein

Urgestein

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →