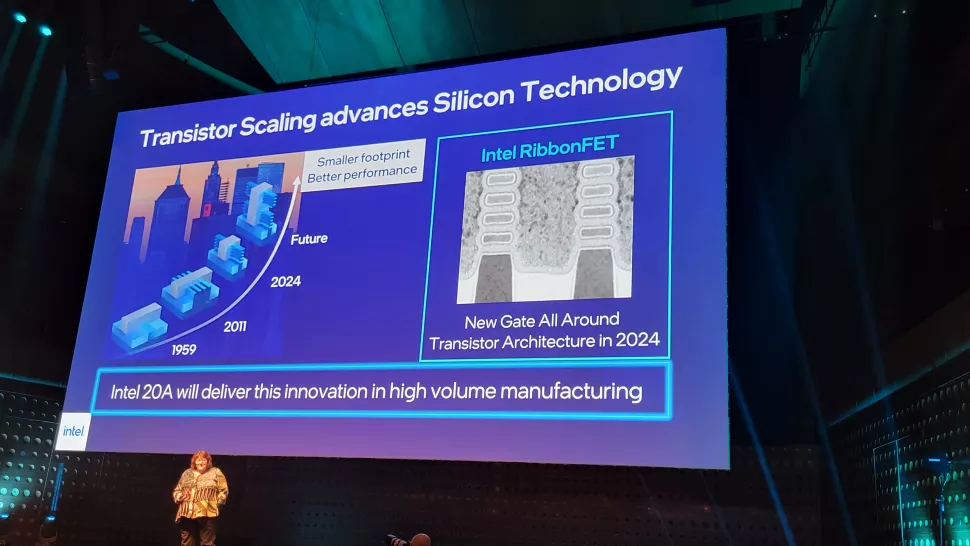

Ann Kelleher, General Manager für Technologieentwicklung bei Intel, präsentierte auf der ITF World 2023 in Antwerpen, Belgien, einen Überblick über die neuesten Entwicklungen des Unternehmens in verschiedenen Schlüsselbereichen. Eine besonders spannende Enthüllung war die zukünftige Verwendung gestapelter CFET-Transistoren durch Intel. Diese Präsentation markierte das erste Mal, dass Intel diesen neuen Transistortyp öffentlich vorstellte. Kelleher gab jedoch keine konkreten Informationen über ein Produktionsdatum oder einen festgelegten Zeitrahmen.

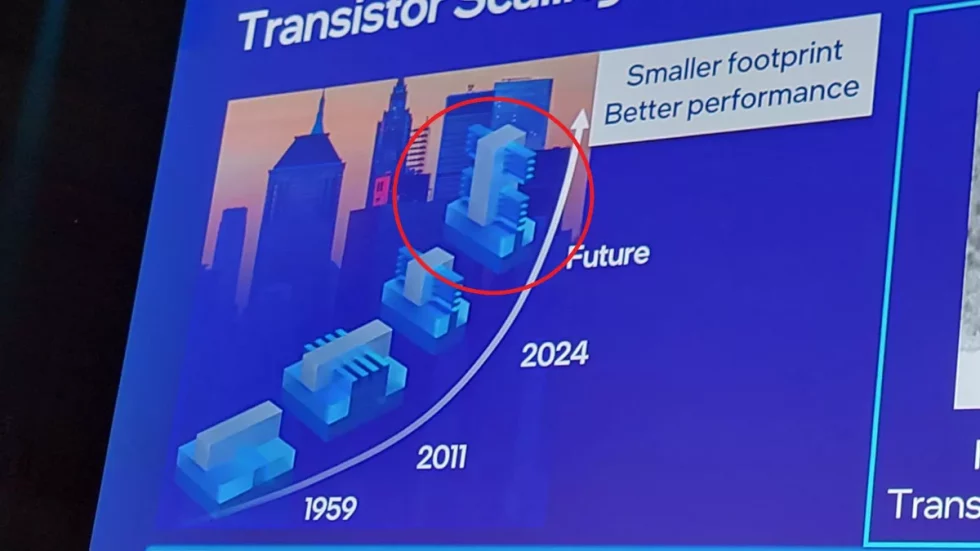

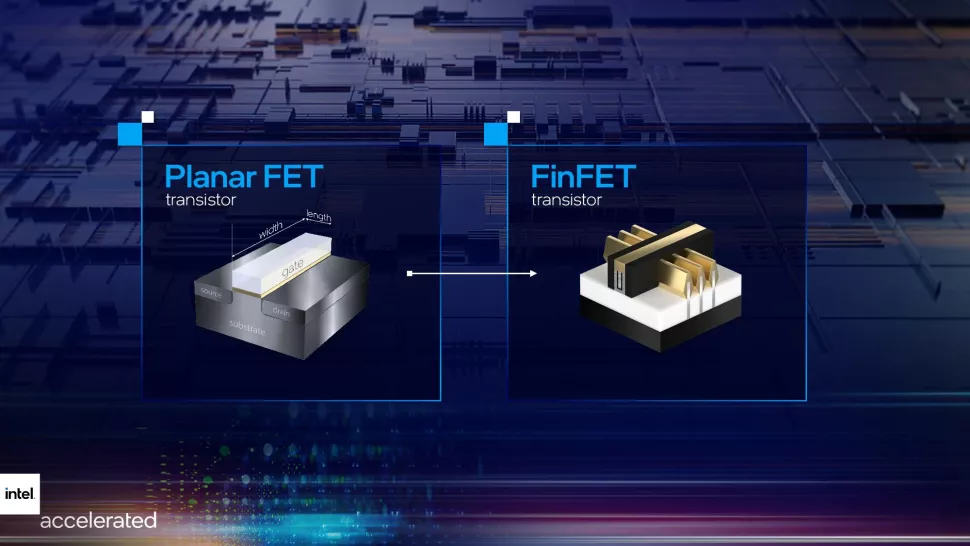

Hier haben wir eine vergrößerte Version der Folie, auf der ein Ring um den neuen Transistortyp zu sehen ist. Die beiden Transistortypen am unteren Rand der Folie sind ältere Varianten, während der Eintrag “2024” für Intels neue RibbonFET-Transistoren steht. Wir haben bereits früher ausführlich über diese Transistoren berichtet. Intels Design der ersten Generation mit dem Prozessknoten “Intel 20A” besteht aus vier gestapelten Nanoblättern, die jeweils vollständig von einem Gate umgeben sind. Laut Kelleher wird dieses Design voraussichtlich 2024 auf den Markt kommen. Der RibbonFET verwendet ein Gate-All-Around-Design (GAA), das sowohl eine höhere Transistordichte als auch Leistungsverbesserungen ermöglicht. Es ermöglicht ein schnelleres Schalten der Transistoren bei gleichem Treiberstrom im Vergleich zu mehreren Finnen, jedoch auf kleinerer Fläche.

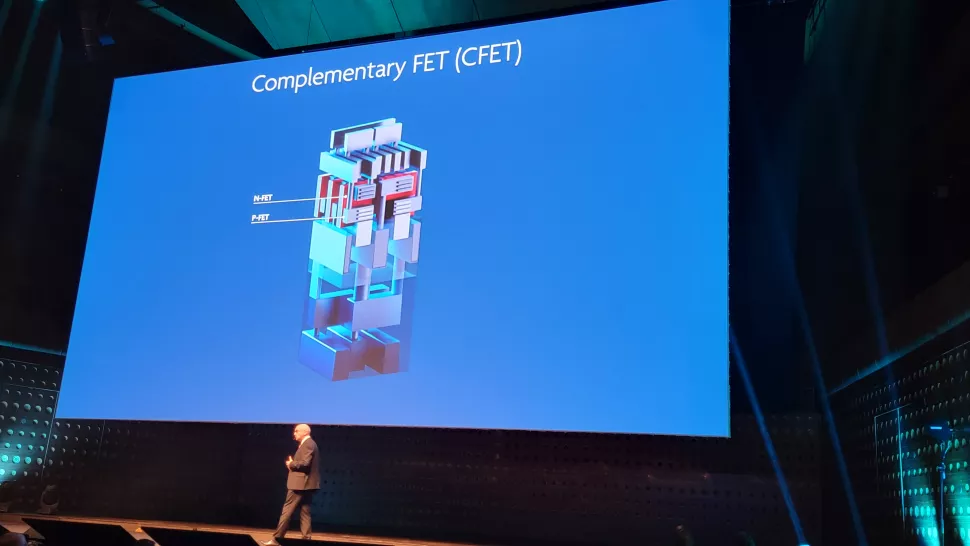

Kellehers Präsentation enthüllt zudem das kommende Generation des Intel GAA-Designs – den gestapelten CFET. Das Transistordesign des Complementary FET (CFET) wird bereits seit einiger Zeit in der Roadmap von imec verfolgt, jedoch haben wir es bisher weder auf einer Intel-Folie gesehen noch davon gehört, dass das Unternehmen die Implementierung dieses Designs plant. Es ist wichtig daran zu erinnern, dass imec ein Forschungsinstitut ist, das zukunftsweisende Technologien erforscht und mit der Industrie an deren Umsetzung zusammenarbeitet.

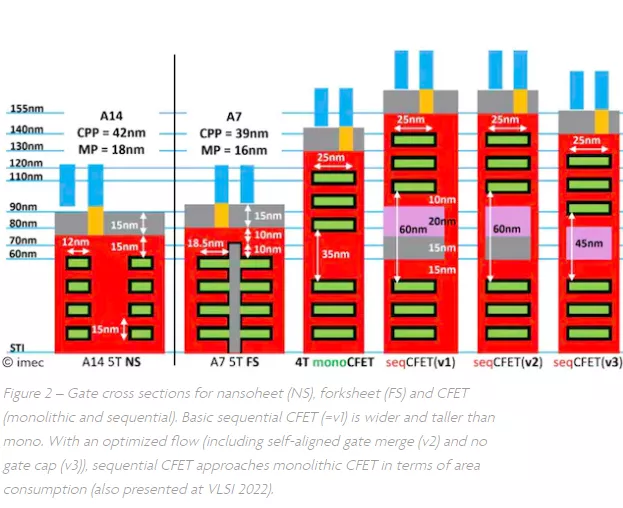

Selbstverständlich gibt es einige Unterschiede zwischen der stilisierten Darstellung von Intel und der CFET-Darstellung von imec, die in dem ersten Bild des vorliegenden Albums hinzugefügt wurden. Dennoch bringt das Bild von Intel die Sache gut auf den Punkt: Das Design ermöglicht es dem Unternehmen, acht Nanosheets übereinander zu stapeln, was eine Verdoppelung im Vergleich zu den vier Nanosheets beim RibbonFET bedeutet und somit die Transistordichte erhöht. Wir haben auch Bilder der drei anderen Arten von Intel-Transistoren in dem oben genannten Album – Planar-FET, FinFET und RibbonFET.

CFET-Transistoren ermöglichen eine höhere Dichte, indem sie n- und pMOS-Bauelemente übereinander stapeln. Es gibt derzeit zwei Arten von CFETs, die erforscht werden: monolithische und sequentielle. Die vier Bauelemente auf der rechten Seite des Bildes zeigen verschiedene vorgeschlagene CFET-Designs. Es ist noch unklar, welches Design Intel übernehmen wird oder ob Intel eine andere Implementierungsart entwickeln wird. Imec hat CFETs erst auf seiner Roadmap, wenn die Chips bis 2032 auf 5 Angström schrumpfen. Daher wird es noch einige Zeit dauern, bis weitere Informationen verfügbar sind. Es gibt keine Garantie, dass Intel CFET in diesem Zeitrahmen anstrebt. Interessanterweise zeigt Intels Folie den GAA-Nanoblech-Transistor der nächsten Generation (RibbonFET) und erwähnt dann CFET, ohne auf die GAA-Gabelblech-Transistoren einzugehen, die von vielen als Zwischenschritt zwischen Nanoblech und CFET betrachtet werden.

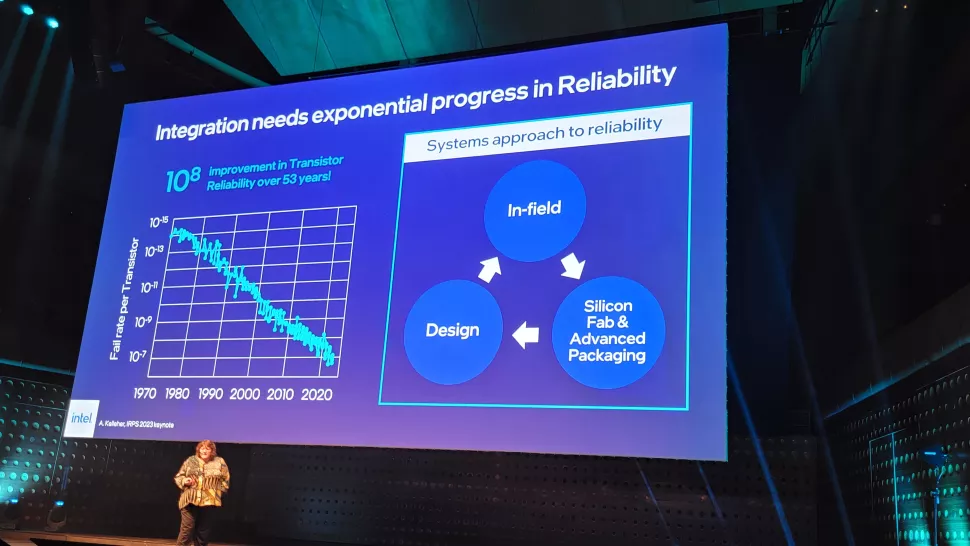

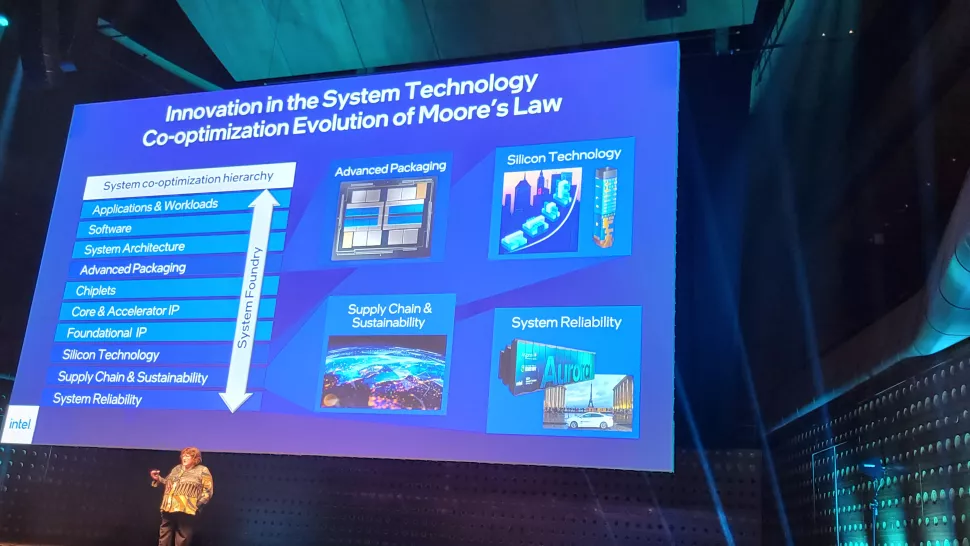

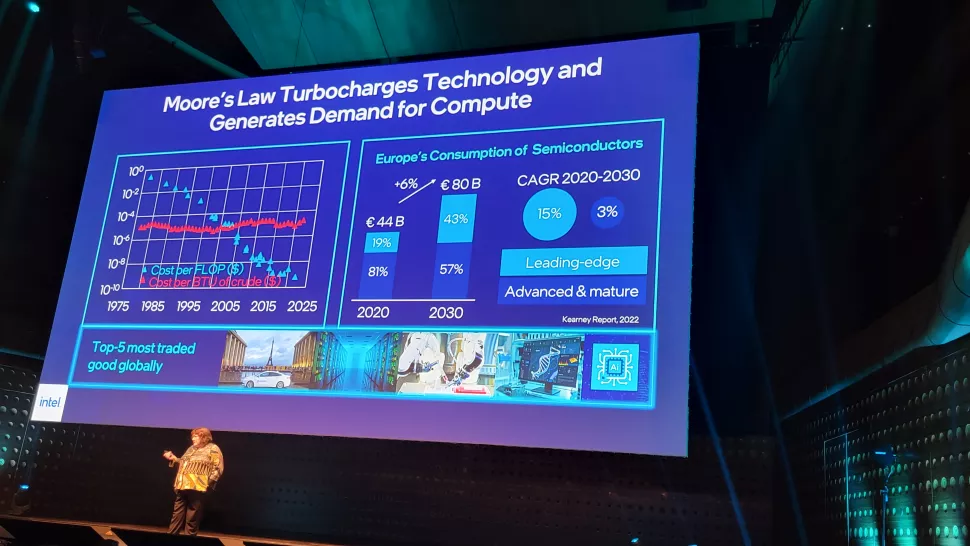

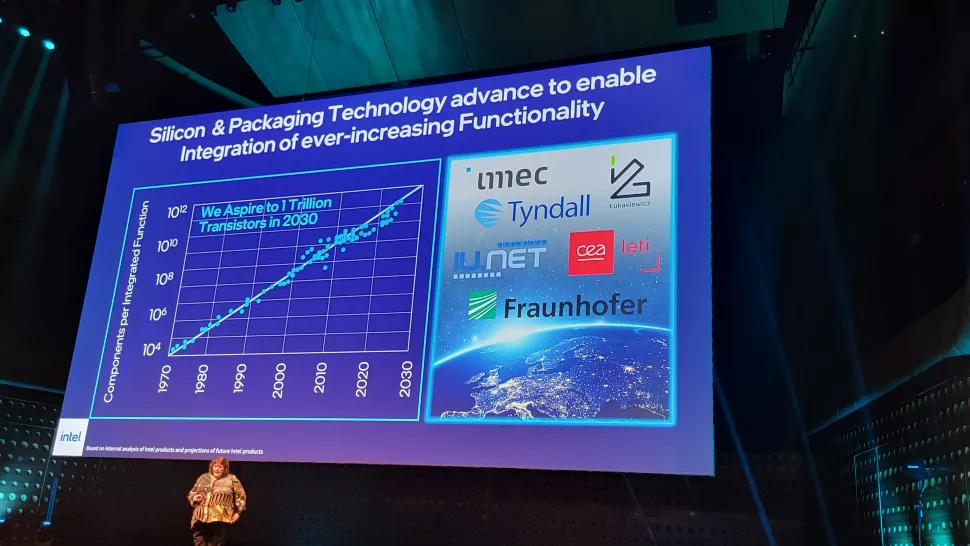

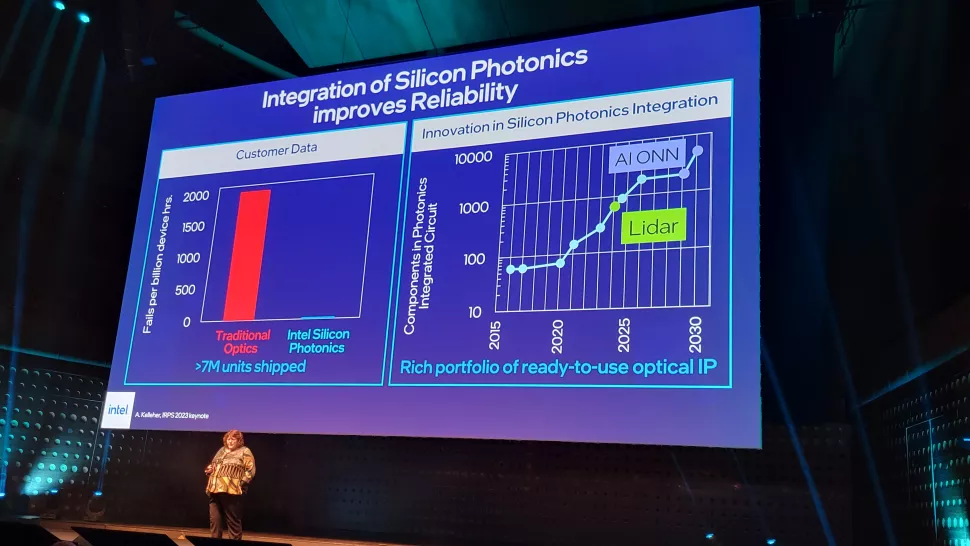

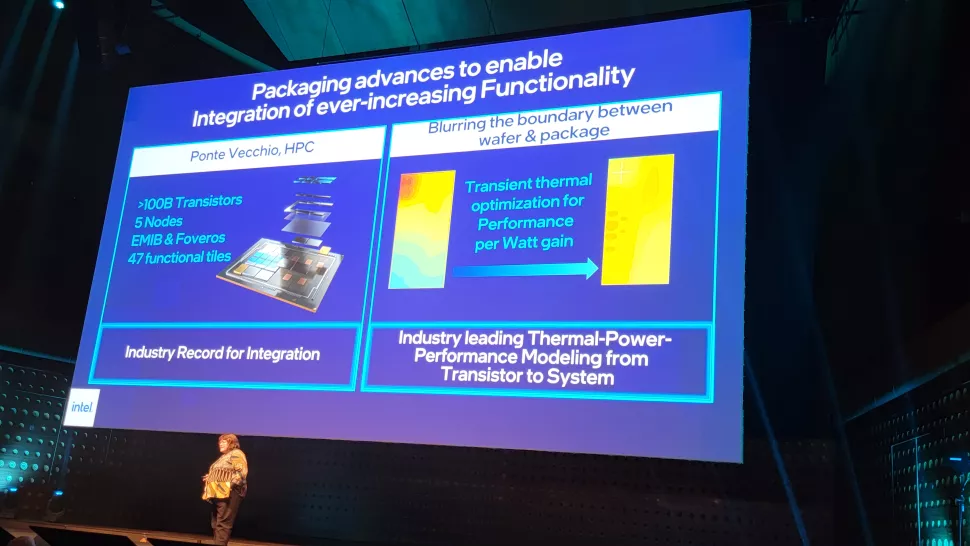

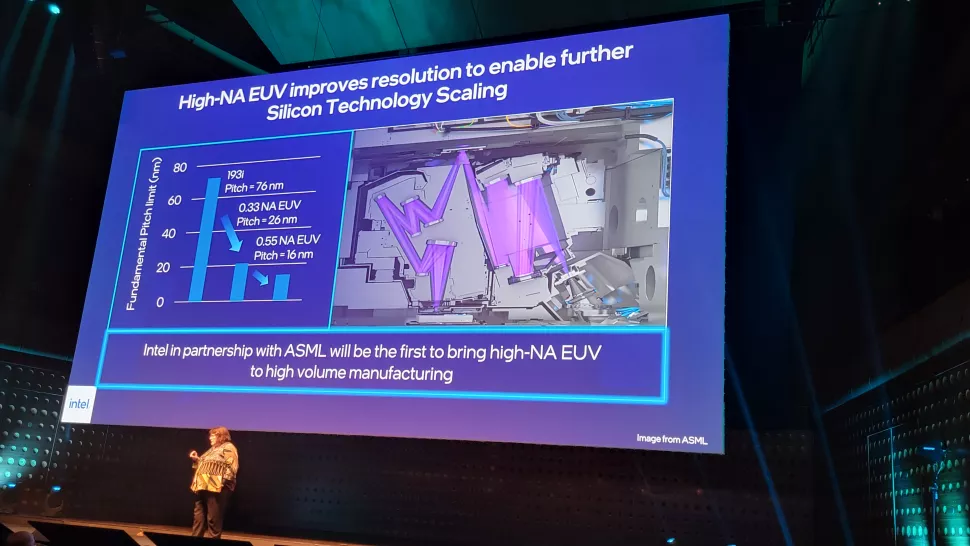

Der zweite Transistortyp auf der Folie ist ein GAA-Gabelblech-Transistor. Da das Bild von Intel nicht sehr detailliert ist, ist es möglich, dass das Unternehmen auch Forksheet-Transistoren plant, bevor es zu CFET übergeht. Es wurden jedoch noch keine Einzelheiten veröffentlicht. Hier sind jetzt auch noch die restlichen Folien des Vortrags von Kelleher, der im Rahmen der ITF World Konferenz des imec stattfand. In seinem Vortrag behandelte Kelleher eine Vielzahl von Themen, darunter den kontinuierlichen Rückgang der Kosten pro Transistor im Laufe der Zeit, die steigende Zuverlässigkeit von Transistoren, die zunehmende Komplexität des Packaging-Prozesses und die Bedeutung des Übergangs zur System Technology Co-Optimization-Methode für Intels Design-Bemühungen.

Kelleher begann seine Rede mit einem Rückblick auf seine eigene Geschichte mit dem imec. Intel unterhält ebenfalls seit über 30 Jahren Beziehungen zum imec, die bis heute andauern. Man kann das imec auch als eine Art “Silizium-Schweiz” betrachten. Es fungiert als wichtiger Eckpfeiler der Branche und bringt harte Konkurrenten wie AMD, Intel, Nvidia, TSMC und Samsung mit Chipherstellern wie ASML und Applied Materials sowie wichtigen Halbleiter-Software-Design-Firmen (EDA) wie Cadence und Synopsys zusammen.

Dabei herrscht ein kooperatives Umfeld, in dem nicht miteinander konkurriert wird. Durch diese Zusammenarbeit können die Unternehmen gemeinsam den Fahrplan für die nächste Generation von Werkzeugen und Software festlegen, die zur Entwicklung und Herstellung der Chips verwendet werden, die unsere Welt antreiben.

Quelle: TomsHardware

Kommentieren