Ann Kelleher, general manager of technology development at Intel, presented an overview of the company’s latest developments in several key areas at ITF World 2023 in Antwerp, Belgium. One particularly exciting revelation was Intel’s future use of stacked CFET transistors. This presentation marked the first time Intel publicly introduced this new type of transistor. However, Kelleher did not provide any specific information about a production date or a set time frame.

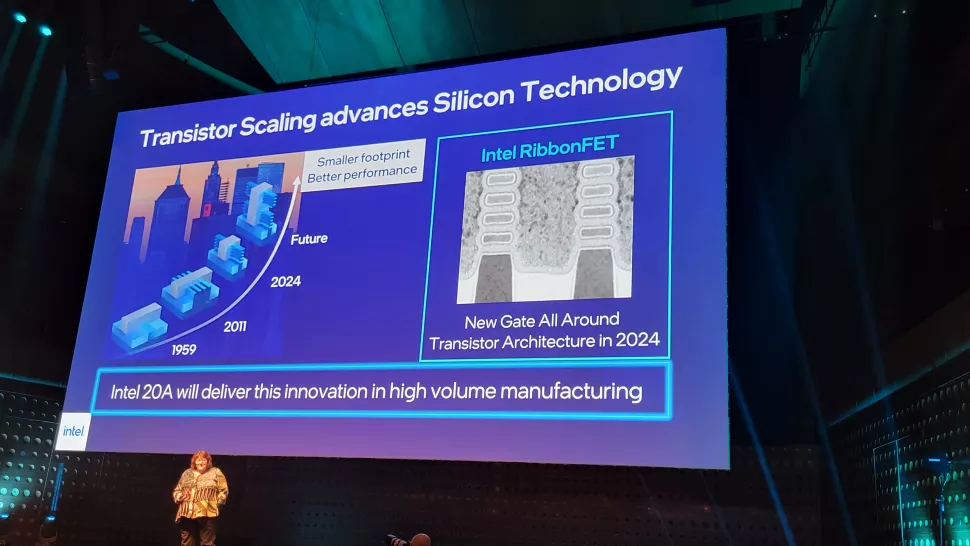

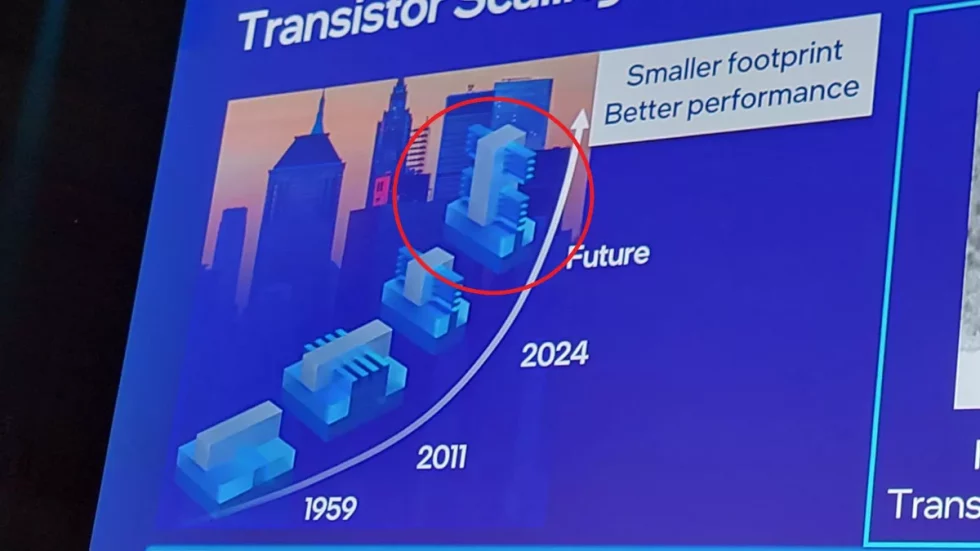

Here we have an enlarged version of the slide showing a ring around the new transistor type. The two transistor types at the bottom of the slide are older variants, while the “2024” entry represents Intel’s new RibbonFET transistors. We have previously reported on these transistors in detail. Intel’s first-generation design, with the process node “Intel 20A,” consists of four stacked nanosheets, each completely surrounded by a gate. According to Kelleher, this design is expected to hit the market in 2024. The RibbonFET uses a gate-all-around (GAA) design that enables both higher transistor density and performance improvements. It enables faster switching of transistors at the same drive current compared to multiple fins, but in a smaller area.

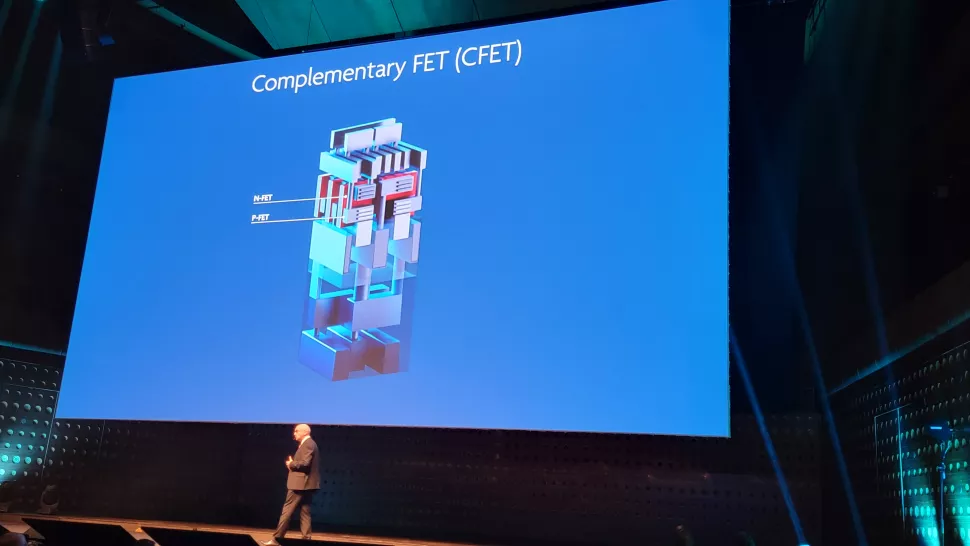

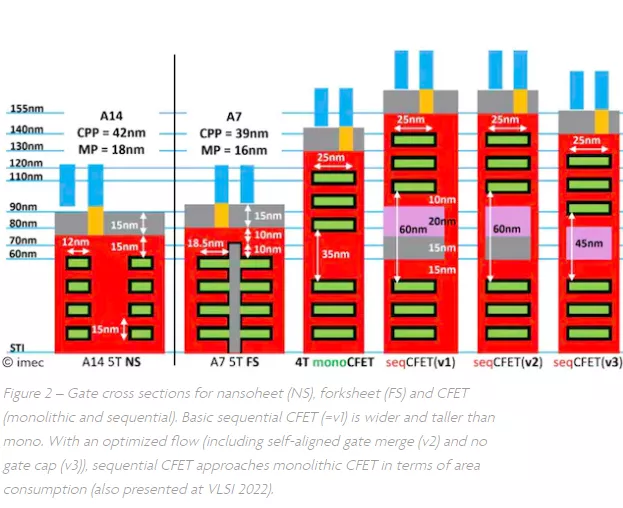

Kelleher’s presentation also reveals the upcoming generation of Intel GAA design – the stacked CFET. The Complementary FET (CFET) transistor design has been tracked in imec’s roadmap for some time, but we have yet to see it on an Intel slide or hear of the company planning to implement it. It is important to remember that imec is a research institute that explores forward-looking technologies and collaborates with industry on their implementation.

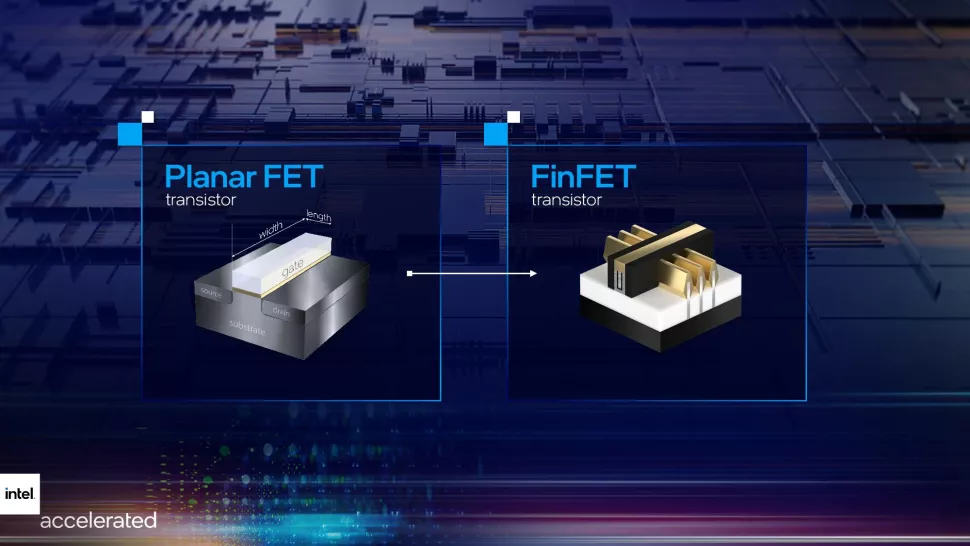

Of course, there are some differences between Intel’s stylized representation and imec’s CFET representation added in the first image of this album. Still, Intel’s image sums things up nicely: the design allows the company to stack eight nanosheets on top of each other, doubling the four nanosheets used in the RibbonFET and thus increasing transistor density. We also have images of the three other types of Intel transistors in the above album – Planar FET, FinFET and RibbonFET.

CFET transistors enable higher density by stacking n and pMOS devices on top of each other. There are currently two types of CFETs being explored: monolithic and sequential. The four devices on the right side of the image show different proposed CFET designs. It is still unclear which design Intel will adopt or whether Intel will develop a different implementation type. Imec does not have CFETs on its roadmap until chips shrink to 5 angstroms by 2032. Therefore, it will be some time before more information is available. There is no guarantee Intel will target CFET in that time frame. Interestingly, Intel’s slide shows the next-generation GAA nanosheet transistor (RibbonFET) and then mentions CFET without mentioning the GAA forked-sheet transistors, which many consider an intermediate step between nanosheet and CFET.

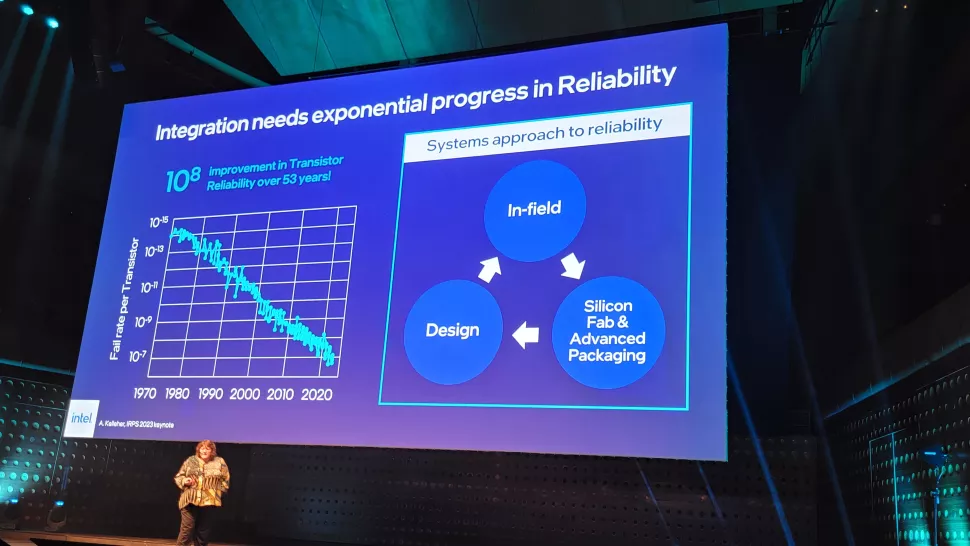

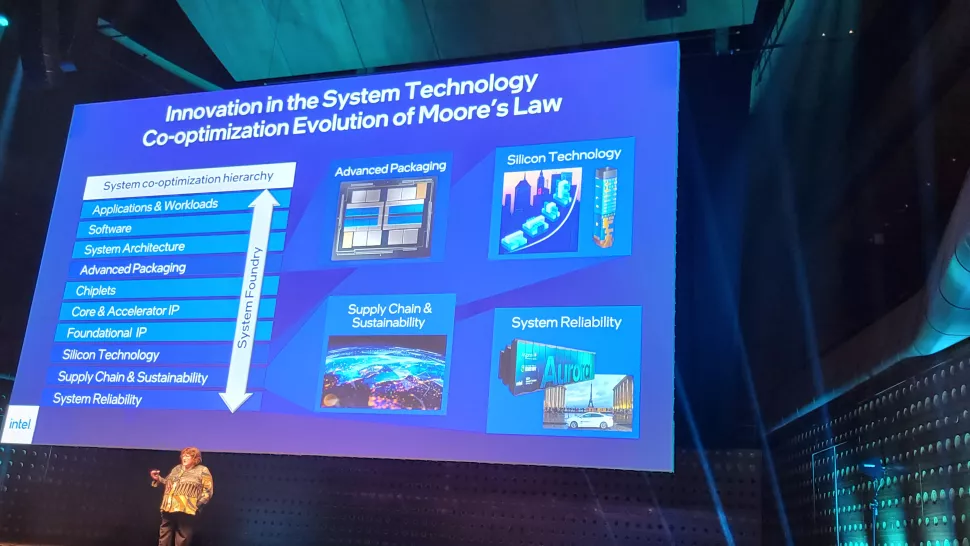

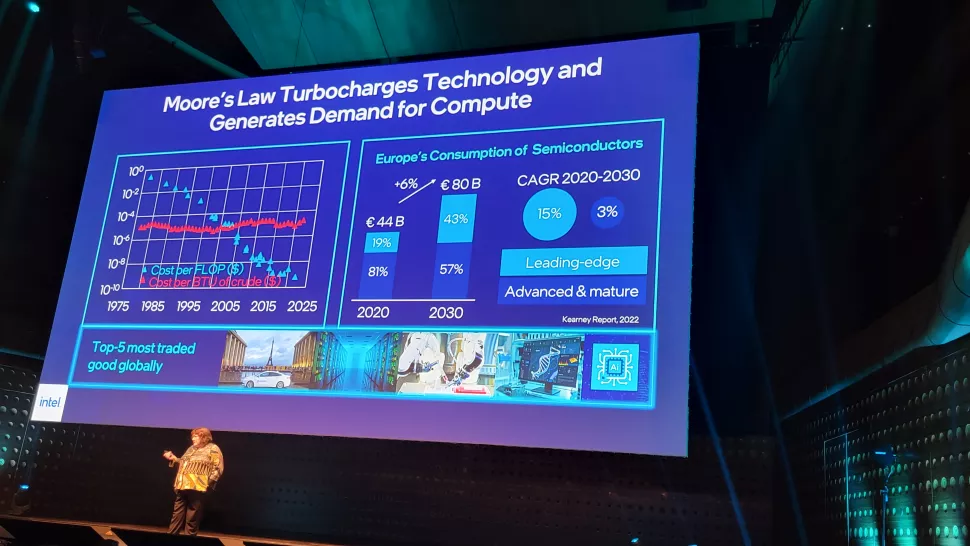

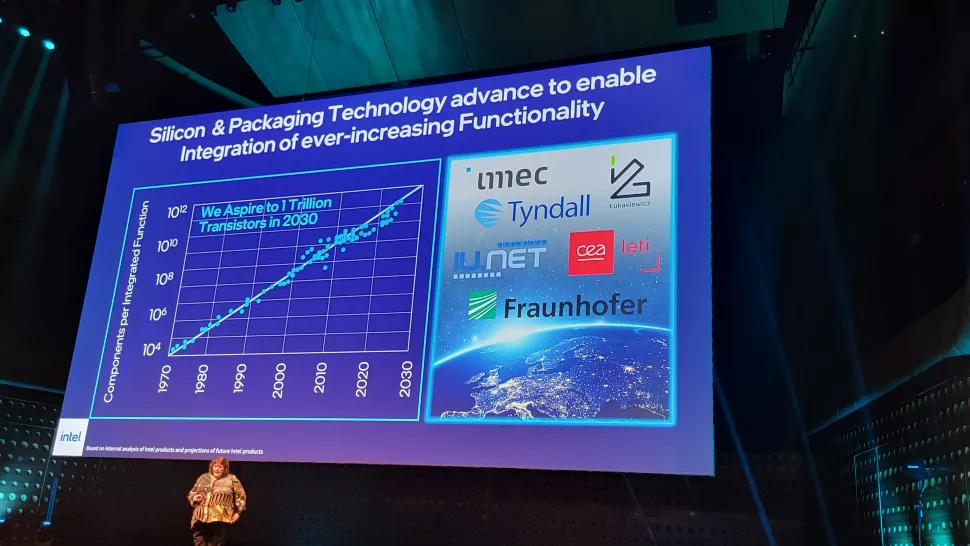

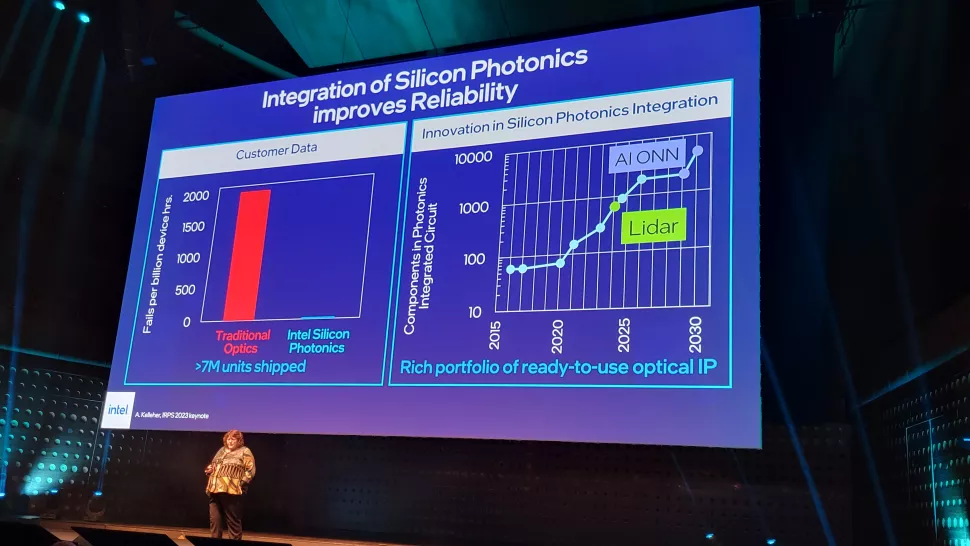

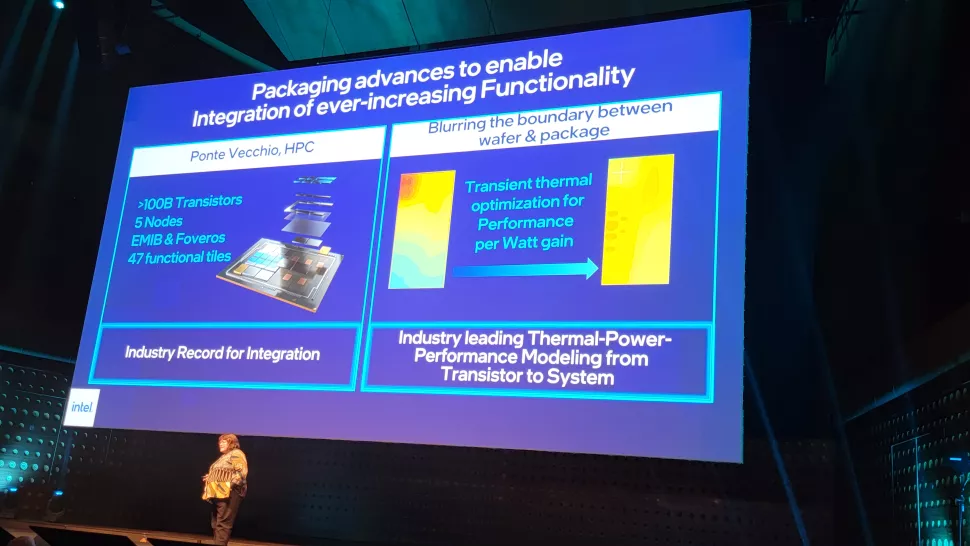

The second transistor type on the slide is a GAA forked-sheet transistor. Since Intel’s image is not very detailed, it is possible that the company is also planning forksheet transistors before moving to CFET. However, no details have been released yet. Now here are the rest of the slides from Kelleher’s talk, which took place at imec’s ITF World conference. In his talk, Kelleher covered a variety of topics, including the steady decline in cost per transistor over time, the increasing reliability of transistors, the increasing complexity of the packaging process, and the importance of the transition to the System Technology Co-Optimization approach to Intel’s design efforts.

Kelleher began his speech by looking back at his own history with imec. Intel has also had a relationship with imec for more than 30 years that continues today. You can also think of imec as a sort of “silicon Switzerland.” It acts as an important cornerstone of the industry, bringing together fierce competitors like AMD, Intel, Nvidia, TSMC and Samsung with chipmakers like ASML and Applied Materials, as well as major semiconductor software design (EDA) firms like Cadence and Synopsys.

This is a collaborative environment where there is no competition. Through this collaboration, the companies can jointly set the roadmap for the next generation of tools and software used to design and manufacture the chips that power our world.

Source: TomsHardware

Kommentieren