Im Support-Dokument von Intel wird erstmals Granite Rapids-D offiziell benannt. Die Xeon D-Modelle werden die Nachfolger von Ice Lake-D sein, die vor einem Jahr als Xeon D-1700 und D-2700 veröffentlicht wurden und zu der Zeit Skylake ersetzten. Es wird erwartet, dass auch Granite Rapids-D spät auf den Markt kommen wird. Intel beschreibt bereits das Featureset der neuen Prozessoren, wobei diese möglicherweise noch Änderungen erfahren werden. Die Server-Prozessoren, bekannt als Granite Rapids-AP und Granite Rapids-SP, werden voraussichtlich ab Ende 2024 erhältlich sein, während die kleineren Xeon D wahrscheinlich nicht vor 2025 erscheinen werden. Das Aufgabenfeld der Prozessoren dürfte sich dabei etwas erweitern. Derzeit finden sie hauptsächlich Anwendung im Kommunikations- und Netzwerksektor, aber auch in vielen Industriebereichen bis hin zum Internet der Dinge (IoT).

> +@item graniterapids-d

> +Intel graniterapids D CPU with 64-bit extensions, MOVBE, MMX, SSE,

SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, CX16, SAHF, FXSR, AVX, XSAVE,

PCLMUL, FSGSBASE, RDRND, F16C, AVX2, BMI, BMI2, LZCNT, FMA, MOVBE, HLE,

RDSEED, ADCX, PREFETCHW, AES, CLFLUSHOPT, XSAVEC, XSAVES, SGX, AVX512F,

AVX512VL, AVX512BW, AVX512DQ, AVX512CD, PKU, AVX512VBMI, AVX512IFMA, SHA,

AVX512VNNI, GFNI, VAES, AVX512VBMI2, VPCLMULQDQ, AVX512BITALG, RDPID,

AVX512VPOPCNTDQ, PCONFIG, WBNOINVD, CLWB, MOVDIRI, MOVDIR64B,

VX512VP2INTERSECT, ENQCMD, CLDEMOTE, PTWRITE, WAITPKG, SERIALIZE,

TSXLDTRK, UINTR, AMX-BF16, AMX-TILE, AMX-INT8, AVX-VNNI, AVX512FP16,

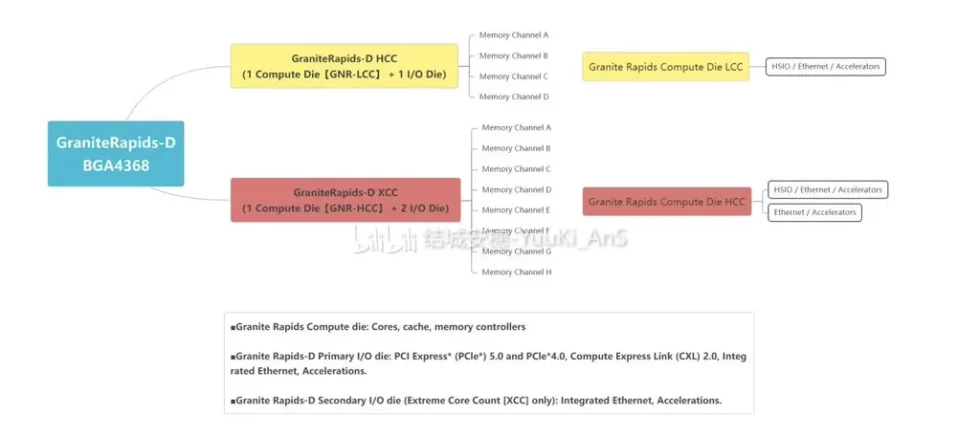

AVX512BF16, AMX-FP16, PREFETCHI and AMX-COMPLEX instruction set support.Nachdem der Stein ins Rollen gebracht wurde, werden prompt weitere Informationen bekannt. Diese zeigen unter anderem, dass Intel erneut zwei grundlegende Chips auflegt: Granite Rapids-D als MCC und XCC, für eine mittlere Anzahl an Kernen oder die höchste Ausbaustufe. Diese basieren jeweils auf dem gleichen Compute-Die des regulären Intel Granite Rapids, wobei entweder die LCC-Version (Low Core Count) oder die HCC-Variante (High Core Count) genutzt wird.

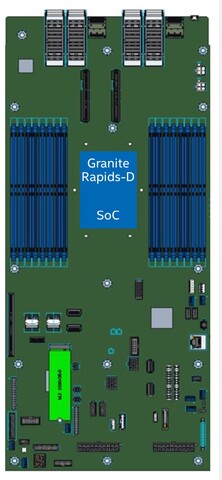

Damit einher geht auch der Ausbau des Speichercontrollers: Das MCC-Modell verfügt über vier Kanäle, während der XCC-Chip acht Speicherkanäle bietet, die aus dem entsprechenden CPU-Die stammen. Ein I/O-Die ermöglicht zudem eine Vielzahl weiterer Anschlüsse, wobei beim XCC-Chip zwei davon verbaut sind. Erste Bilder von geplanten Mainboards bestätigen diese Informationen.

Quelle: ComputerBase

2 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Veteran

Alle Kommentare lesen unter igor´sLAB Community →