The Phison PS5019-E19T just described is compatible with a wide range of flash memory variants and supports modern NAND chips with 1200 MHz interface. And because it’s so nicely compatible, if you’re a low-cost NVMe SSD vendor, you can also use Micron’s latest 176-layer TLC 3D NAND (codenamed B47R) with it. For example, the MSI Spatium M450 I tested contains two IABHG94AYA chips, each with eight 512-gigabit TLC 3D NAND blocks inside.

By the way, Micron’s still quite new 176-layer flash is the first real in-house development by Micron after the separation from Intel. This memory is also very different in its internal structure from the products of all other manufacturers. The cell structure of the Micron NAND relies on replacement gate, which ends up being a cross between floating gate and charge trap technologies. Micron replaced the polysilicon in the gate material with metal in this NAND and switched to a different process for etching the vertical cylindrical channel, resulting in an increased diameter.

In addition, a non-conductive layer of silicon nitride has been introduced into the structure of the micron memory, in which data can be stored. This layer also reduces quite effectively the mutual interference of the cells in such a vertical stack. How the stack works is explained in a video from Micron that is so trivial that it is worth watching. Of course, I do not want to withhold this from you:

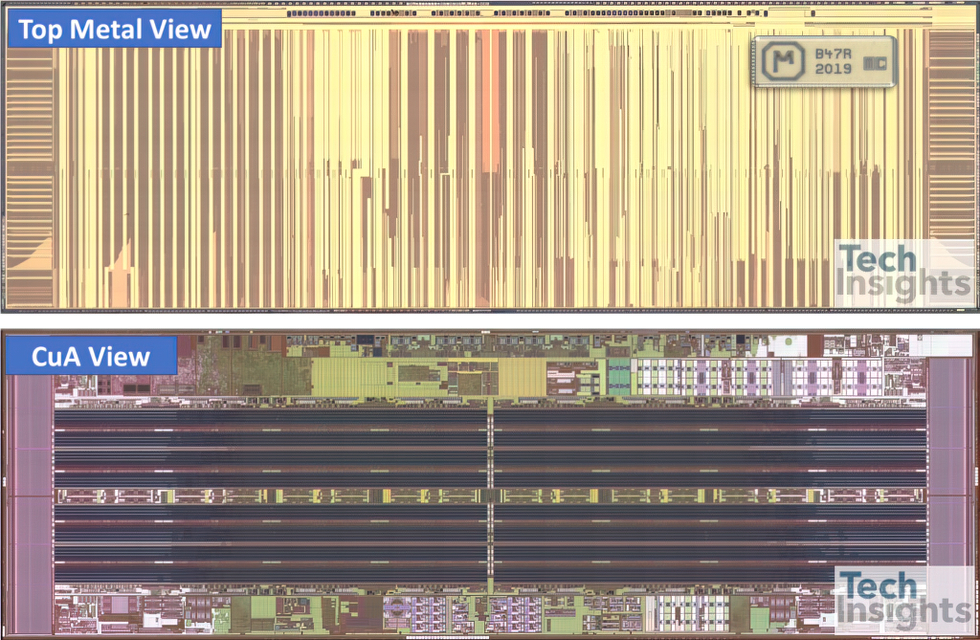

Of course, we can go into a little more detail. The next figure shows a chip looking at the metal top, a chip looking at the CMOS circuits (CuA) and the markings of the B47R chip. Compared to the older B37R TLC die, the chip size has been reduced by a whopping 25% due to the higher cell density, larger number of 3D NAND cells and effective scaling of the design. The B47R is now Micron’s second generation CTF structure after the B37R.

The height of the NAND cell array (for comparison: the height from the selector on the source side to the BL) is now more than 11 µm. The total number of gates, including selectors (STs) and dummy word lines (DWLs) per vertical NAND strand is 195, or 195T, which is the highest number ever achieved in 3D NAND. They rely on double-stack architecture, the replacement gate process, charger trap nitride (CTN) and CMOS-under-array (CuA) techniques. The bit density reaches 10.273 Gb/mm2 for the 512Gb TLC die.

Thus, in the end, it was possible to achieve a number of positive effects, because it was possible to increase the speed of the programming cells, increase their stability, reduce power consumption and at the same time also improve the reliability of data storage. Ultimately, Micron’s 176-layer TLC-3D NAND thus takes the next step in 3D flash technology in general. And in terms of performance, Micron claims that the new memory has reduced read and write latency by about 35% compared to the previous generation 96-layer memory. Well….

22 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Mitglied

Urgestein

1

Mitglied

Mitglied

1

Veteran

Moderator

Mitglied

1

1

Moderator

Veteran

1

Mitglied

Mitglied

Mitglied

Alle Kommentare lesen unter igor´sLAB Community →