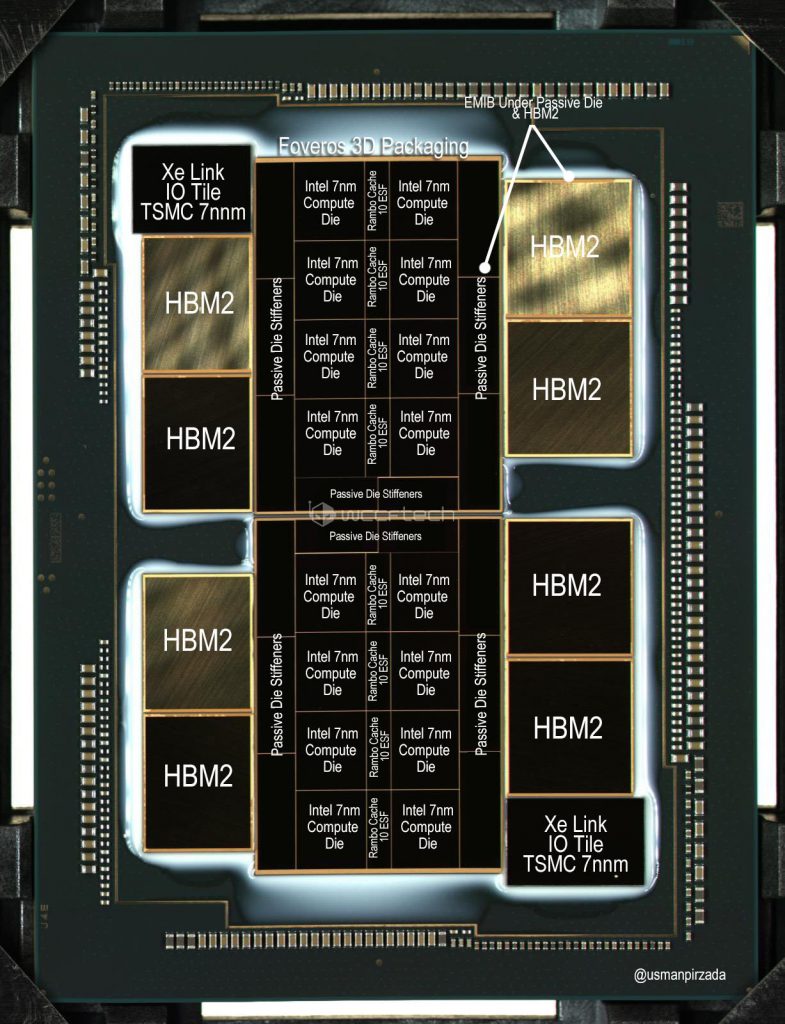

Intel hat kürzlich einen der größten Chips vorgestellt, und die Kollegen von wccftech.com haben diverse Quellen für weitere Details angezapft. Obwohl es ja aufgrund der technischen Erläuterungen auf Intels Architecture Day in ungefähr klar war, was Intel da vorhat, ist das Bild, das sich nun ergibt, durchaus überwältigend. Die Kollegen zeigen erstmalig Intels 7nm Die Shot (eines gepackten Produkts) samt einer vollständigen und korrekten Beschriftung dessen, was einen demnächst wohl erwarten wird.

Intels Xe HPC 2-Tile (PVC) GPU verwendet hierfür eine Mischung aus Intels 7nm, Intels 10nm ESF und TSMCs 7nm Prozesstechnologie, die im Foveros-3D-Packaging zusammengeführt wurde. Alles, was die Kollegen in ihrem Artikel erwähnt haben, wurde von mindestens zwei ihrer Quellen bestätigt sowie mit Querverweisen versehen und stellt die korrekte Beschriftung für den Xe HPC Die Shot dar. Das von Intels Chefarchitekten Raja Koduri gezeigte Intel Xe HPC 2-Tile-Paket (was so ziemlich der Ponte Vecchio GPU in ihrem frühen Stadium entspricht) ist ein absolutes Wunderwerk in Bezug auf die verwendete Technologie.

Der Die-Shot ist nichts weniger als eine technische Demonstration von Intels fortschrittlichsten Prozess- und Packaging-Technologien. Er zeigt nicht nur den allerersten 7nm-Die (in einem gepackten Produkt) von Intels hauseigenem 7-nm-Prozess, sondern er zeigt auch EMIB im Einsatz zusammen mit Foveros 3D-Packaging. Man erkennt auch die versprochene Mix-and-Match-Philosophie mit Teilen von TSMC und neuen Features wie z.B. Rambo Cache.

Fangen wir von oben an. Das Xe Link/IO Tile ist in der oberen linken und unteren rechten Ecke des Gehäuses zu sehen und wurde im 7-nm-Prozess von TSMC gefertigt. Interessanterweise enthält der Die Shot auch zwei unterschiedlich große HBM2-Tiles, die auf beiden Seiten der Haupt-Tiles zu sehen sind. Im Mittelpunkt der beiden Kacheln steht natürlich der Compute-Die (16 insgesamt), der in Intels eigenem 7-nm-Prozess gefertigt wird. Die Annahme, dass die vertikalen Dies, die den Compute Die umgeben, entweder ein XEMF Scalable Memory Fabric oder Rambo Cache sind, sind so nicht wahr. Die vertikalen Dies auf der rechten, linken, oberen und unteren Position sind in Wahrheit nur passive Die-Versteifungen, die jedoch keine Logik enthalten.

Der Rambo Cache befindet sich tatsächlich in der Mitte und wird auf Intels 10 nm Enhanced Super Fin Prozess gefertigt. Der 10-nm-Basis-Die befindet sich tatsächlich unter den Kacheln, die man auf dem Bild sehen kann. EMIB befindet sich unter den passiven Dies und dem HBM2. Da dieses Package auf Intels 3D-Foveros Technologie setzt, ist hier noch vieles verdeckt und verborgen und solange man kein detailliertes 3D-Diagramm mit den einzelnen Schichten erhält, lässt sich die Komplexizität das Packagages nur erahnen

Raja verriet ja bereits, dass hier 7 fortschrittliche Technologien im Spiel sind, und die Kollegen interpretieren dies so:

- Intel 7nm

- TSMC 7nm

- Foveros 3D-Packaging

- EMIB

- Verbesserte Super Fin

- Rambo-Cache

- HBM2

Man muss allerdings auch bedenken, dass das gezeigte Package lediglich die erste Iteration (also ein Prototyp) von Intels kommendem Ponte Vecchio-Chip ist. Wenn man mit berücksichtigt, dass dieser irgendwann Ende 2021 oder Anfang 2022 erscheinen soll, zeigt dieses Lebenszeichen, dass das Unternehmen auf einem guten Weg zu sein scheint, was die eigene Roadmap angeht. Ponte Vecchio wird im Supercomputer Aurora zum Einsatz kommen und es gab im Vorfeld durchaus viele Bedenken, ob Intel den Termin überhaupt einhalten kann. Die Antwort darauf, so scheint es, ist allerdings ja.

Quelle: wccftech.com

17 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Veteran

1

Mitglied

Mitglied

1

Veteran

Veteran

Mitglied

Veteran

Veteran

Mitglied

Urgestein

Veteran

Veteran

Urgestein

1

Alle Kommentare lesen unter igor´sLAB Community →