Die Halbleiterindustrie erfreut sich eines steigen Wachstums, obwohl ein Mangel an Chips mittlerweile alles vom Auto bis zum Küchengerät plagt. Doch während die Chips selbst immer schneller und intelligenter werden, hat sich der Prozess der Chipentwicklung selbst in den letzten 20 Jahren nicht wesentlich verändert. In der Regel dauert es 2 bis 3 Jahre, einen Chip mit einem großen Ingenieurteam zu entwerfen und es kostet Dutzende oder Hunderte von Millionen Dollar, einen Chip von der Idee bis zur Fertigung zu bringen.

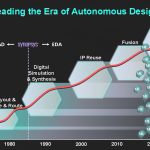

Doch kündigt sich der Wandel in Form von künstlicher Intelligenz an, die vor kurzem erhebliche Verbesserungen bei der Optimierung von Layouts für Stromverbrauch, Fläche (Kosten) und Leistung gezeigt hat. Mit Hilfe eines auf Reinforcement Learning (RL) basierenden Ansatzes, ähnlich dem, der 2016 den GO-Weltmeister besiegt hat, gab Samsung bekannt, dass man jetzt einen Chip aus der Fabrik zurückbekommen haben, der mit der DSO.ai-Plattform von Synopsys optimiert wurde. Soweit bekannt, ist dies auch der erste funktionierende Chip der Branche überhaupt, dessen Layout von KI entworfen wurde.

Synopsys geht davon aus, dass nunmehr ein großer Teil der Halbleiterindustrie anfangen wird, diese KI-Plattformen zu nutzen, denn die Auswirkungen sind einfach zu groß, um sie zu ignorieren. Tatsächlich ist der EDA-Anbieter Cadence Design Systems kürzlich dem Beispiel von Synopsys gefolgt und hat KI-Tools eingeführt, die Leistung, Stromverbrauch, Kosten und Design drastisch verbessern können. Mit der Unterstützung von Designteams, die bessere Chips in deutlich kürzerer Zeit produzieren, lässt sich nämlich auch viel Geld verdienen. Nachfolgend habe ich für Euch noch die Folien der heutigen Präsentation, bevor wir noch etwas tiefer ins Thema einsteigen wollen:

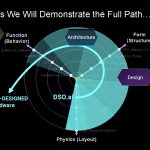

Obwohl Synopsys einen Vorsprung von mindestens 16 Monaten gegenüber der Konkurrenz zu haben scheint, geht das Unternehmen jetzt bereits den nächsten Schritt und hat in einer Grundsatzrede vor den Teilnehmern der jährlichen Hot Chips-Konferenz die Visionionen des Unternehmens veranschaulicht. Synopsys plant den Einsatz neuer KI, um neben den bereits mit DSO.ai realisierten Aspekten des physikalischen Designs auch andere Elemente des Workflows zu optimieren. Die Ergebnisse könnten die Branche durchaus verändern, denn diese Fortschritte sind ein weiterer Baustein in einer reichhaltigen Wertschöpfungskette, die es noch zu erschließen gilt.

Der Technologieansatz, den Synopsys bei “Place and Route” verwendet hat, wude mittlerweile von NVIDIA, Google und seit kurzem auch vom Konkurrenten Cadence Design Systems aufgegriffen. Die von NVIDIA und Google durchgeführten Forschungsarbeiten sind dabei recht vielversprechend. Man vermutet, dass die meisten Halbleiterunternehmen bald KI einsetzen werden, um die Qualität und die Markteinführungszeit zu verbessern, während diejenigen, die dies nicht tun, ins Hintertreffen geraten dürften.

![]()

Ein Blick auf die Abbildung oben zeigt, dass die Arbeit von NVIDIA und Google, die sich auf das Floorplanning (roter Kreis) konzentrierte, die Leistung, Fläche und Frequenz ihrer Chips im Vergleich zu dem, was die Designer durch manuelles Experimentieren erreichen konnten, erheblich verbesserte. Das Floor-Planning ist schließlich eines der vielen NP-schweren Probleme in der EDA und kann aufgrund des großen Suchraums potenzieller Lösungen nicht analytisch gelöst werden. Je nach Ansatz kann diese Suche eine unglaubliche Menge an Rechenleistung erfordern. Während beim GO-Spiel 10360 mögliche Züge ausgewertet wurden, gibt es beim Chip-Design 1.090.000 Möglichkeiten für die Platzierung und Verlegung. Aber das physikalische Design stellt nur die Spitze des Eisbergs dar, wenn es um Optimierungsbereiche geht. Synopsys möchte die Möglichkeiten in Betracht ziehen, die sich ergeben, wenn man den Blick auf einen größeren Teil des Designprozesses richtet. Wenn die Vision von Synopsys richtig ist, und davon ist man dort überzeugt, stehen wir an der Schwelle zu einer Revolution im Chipdesign.

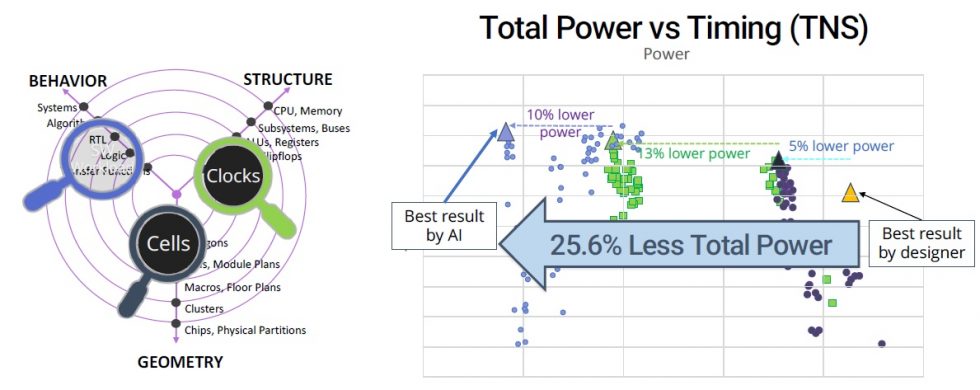

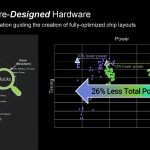

Kann die KI den Menschen ersetzen?

Synopsys und verschiedene Forscher glauben, dass in Zukunft viele weitere Aspekte des Designs durch KI unterstützt werden. Durch die gleichzeitige Anwendung von KI-Optimierung auf allen drei Design-Achsen konnte Synopsys eine interessante Fall-Studie präsentieren die zeigt, dass der Stromverbrauch durch den Einsatz von KI im gesamten Designbereich erheblich gesenkt werden konnte. Die Optimierung der ersten Domäne (Geometrie) mit dem DSO.ai-Produkt der ersten Generation von Synopsys kann den Stromverbrauch um bis zu 5 % im Vergleich zu dem reduzieren, was ein Designteam ohne KI erreichen könnte.

Hier kommt die Technologie der zweiten Generation ins Spiel: Durch Hinzufügen der strukturellen Exploration zur Geometrie, d. h. durch die gleichzeitige Erkundung verschiedener architektonischer Auswahlpunkte und zugehöriger physikalischer Layouts für jeden dieser Punkte, kann der Stromverbrauch um weitere 13 % reduziert werden. Schließlich wendet sich die KI dem Verhalten zu und nutzt die Software-Workloads selbst, um den Stromverbrauch des Chips – wiederum gleichzeitig mit Architektur und Layout – um weitere 10 % zu optimieren. Nimmt man alles zusammen, könnte man den Stromverbrauch um fast unglaubliche 26 % senken, verglichen mit dem besten Ergebnis eines talentierten Chipdesigners.

Traditionelle Planungsansätze beschränken die Interaktion auf aufeinander folgende Schritte in einem weitgehend linearen Arbeitsablauf. Der architektonische Entwurf diktiert den strukturellen Entwurf, der dann eine Rückkopplungsschleife zum Architekturteam bilden kann. In ähnlicher Weise bestimmt der strukturelle Entwurf die Anforderungen an den logischen Entwurf. Probleme und Möglichkeiten, die bei der Auswahl des Logikdesigns aufgedeckt werden, können die Abwägung mit dem Strukturteam beeinflussen, und so weiter. Dieser Ansatz, der in der Halbleiterindustrie gut verstanden und angenommen wird, schränkt die Optionen ein, die für den gesamten Chip in Betracht gezogen werden, und begrenzt folglich das Ausmaß der in Betracht gezogenen Optimalität.

Der Ansatz von Synopsys ersetzt dieses Modell im Wesentlichen durch einen ganzheitlichen Designansatz, der durch KI unterstützt wird. Synopsys verweist auf einen neuen “Cyclone”-Ansatz, der im Wesentlichen einen Zyklus von gleichzeitig bewerteten Designoptionen schafft. Diese “Optionalität” speist eine breite Palette von Lösungen, die gleichzeitig mit KI modelliert werden, um die Auswirkungen auf Leistung, Stromverbrauch und Die-Fläche zu bewerten. Dieser Ansatz, bei dem Synopsys Pionierarbeit geleistet hat, scheint zu besseren, global optimierten Ergebnissen zu führen (geringerer Stromverbrauch, höhere Leistung, geringere Die-Größe). Der eigentliche Vorteil des neuen Ansatzes für Halbleiterunternehmen liegt jedoch in der deutlich reduzierten Entwicklungszeit. Mit der weiteren Implementierung und Verfeinerung des Ansatzes ist zu erwarten, dass immer mehr Designteams das Potenzial der KI-Designunterstützung nutzen werden.

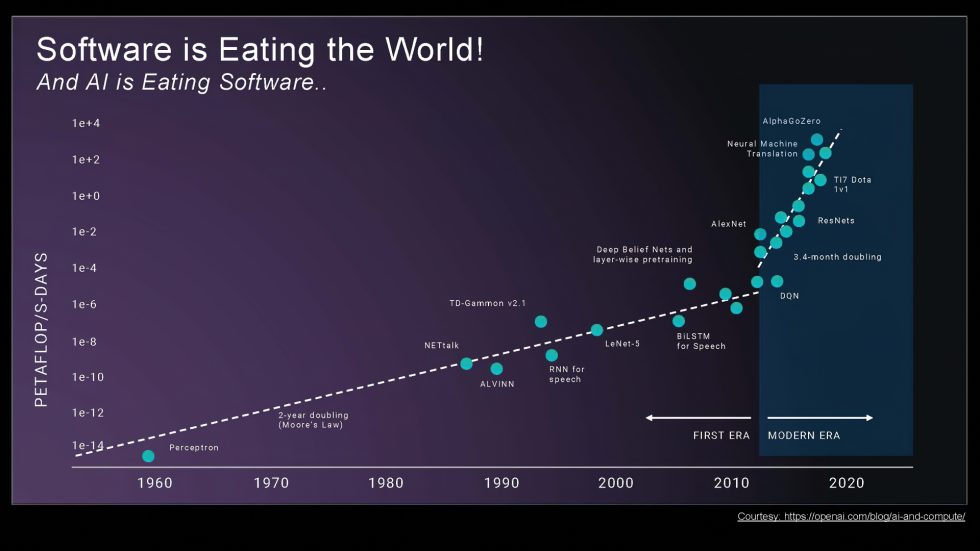

Die Software frisst die Welt, aber es ist die KI, die jetzt die Software frisst. Da immer mehr Softwareanwendungen datengesteuert werden und neuronale Netze bereits die Billionen-Neuronen-Marke überschreiten, stellt sich die Frage, wie die Halbleiterindustrie die für die KI erforderlichen Petaflop-Monate an Rechenleistung vom Rechenzentrum bis zum Endgerät bereitstellen soll. Software-definierte Hardware wurde von Branchenkennern als elegante Lösung vorgeschlagen. Sie basiert auf der Prämisse, dass Chips an die Bedürfnisse bestimmter Anwendungen angepasst werden können, indem Software die direkte Kontrolle über die Befehlssatzarchitektur (ISA), die Chipstruktur (Mikroarchitektur) und die Implementierungsmethode (Siliziumtechnologie) erhält. Die Personalisierung von Chips könnte eine 1.000-fach bessere Leistung und Energieeffizienz bringen, aber hier liegt das Problem: Es dauert derzeit 2 bis 3 Jahre, bis eine neue Idee in einen tatsächlichen Sockel umgesetzt wird.

Die KI könnte die Antwort sein. KI-gesteuerte Designsysteme haben die Produktivität erhöht, um monatelange Designaufgaben auf wenige Tage zu verkürzen. Mit der bevorstehenden globalen Optimierung auf Systemebene könnte man in der Lage sein, neue, personalisierte Chips in nur wenigen Wochen zu entwickeln. Mehr KI im Designprozess könnte in der Tat die Ausweitung des Konzepts der softwaredefinierten Hardware auf softwaredesignte Hardware ermöglichen, was es sowohl möglich als auch wirtschaftlich attraktiv machen würde, viele verschiedene Arten der Beschleunigung zu liefern, um den Anforderungen der kompliziertesten Anwendungen gerecht zu werden.

Source: Synopsis

26 Antworten

Kommentar

Lade neue Kommentare

Urgestein

1

Urgestein

Mitglied

Urgestein

Neuling

Urgestein

Neuling

Urgestein

Neuling

Urgestein

Neuling

Urgestein

Veteran

Urgestein

Urgestein

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →