Well, with this description I dare to take a deep grip into the speculation collection, but let’s look at the whole thing in a sporty and exemplary way, because somehow you have to call this thing (for now). We’re talking about AMD’s new 16-core (32 threads), which is materializing more and more and thus of course leaves traces to be found.

I had already reported exclusively about the B0-Stepping, but the current OPN, so to speak the order numbers of the CPU, give more reason for joy and of course for a new news. So (once again) I do the i-machi and share the latest findings with you. So a little bit of click-bait in the title is allowed, because it is exclusive content and the sources are, as so often, my own.

More boost clock and a solid basic clock

Let us first come to the beat, that is, what most people are interested in in the first place. What can be ordered for testing from the relevant companies is called 100-000000059-52_48/35_Y. Well, the first part of the OPN is not new, I had already published it, but at the end there is the classification for the clock rates. And that’s exactly what up to 4.8 GHz boost clock at 3.5 GHz base clock for all 16 cores looks quite good.

100-000000059-52_48/35_Y

This should bring the clock rates closer to the final maximum, because it’s not too long until the launch is announced and at some point the finished samples will have to be tested thoroughly. But there are several reasons how to reach the 4.8 GHz now, but I have one of them exclusively for you, because there will also be a new playground for overclockers. But more on that in a moment.

New features and an interesting changelog

When Intel introduced the CPUs of the 10. generation one of the accompanying innovations was the separate Vcore optimization for each individual core (also via software), i.e. what is called per core voltage adjustments. This is exactly how Intel managed to squeeze a really acceptable performance out of an actually old and inferior structure width. This feature will also be interesting for overclockers and it will be interesting to see how the feature will be integrated into the Ryzen Master Tool.

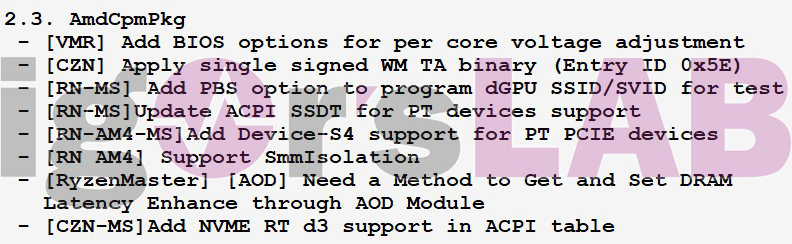

Exactly there AMD will now start analogous to Intel, as the Changelog ComboAM4v2PI 1.0.6.0 tells us, even if one has internally already arrived at revision 8. I already explained the meaning of the numbers of the respective minors in the article “AMD UEFI Inside: What is really behind AGESA, the PSP (Platform Security Processor) and especially ComboPI?“

Interesting here is the first entry, which describes exactly this function. The abbreviations in square brackets stand for the respective chips, i.e. VMR for Vermeer, RN for Renoir etc. The entry for Cezanne (CZN) finally reveals that there seem to be already running copies for this APU.

Furthermore, per port TXCLK gating can also be found in the firmware, which indicates an increase in efficiency. Intelligent clock control techniques are often used to minimize activity in those parts of a circuit that do not contribute to the overall result for that particular clock cycle. This clock control reduces dynamic performance by preventing circuit logic that is not used in a particular clock cycle from switching to that cycle in the first place.

In addition, it prevents clocking in cases where no new data is generated or where this data does not need to be used by the subsequent logic in a particular clock cycle. These gating techniques thus lead to significantly lower dynamics and total power consumption of a circuit at partial loads.

The new BIOS entry Enable VCN/FCLK deep sleep, another energy saving option that was not assigned to any specific model, and therefore might even benefit all CPUs and APUs in the future. If VCN stands for Video Core Next, then this also affects APUs with integrated graphics unit as an additional feature.

The entry Add NVME RT d3 support is also very interesting, because in the state Runtime D3 (RTD3) the controller of the NVMe drive is disconnected from the actual operating voltage. Additional supply voltages may or may not be provided (“aux power”). For PCI Express, RTD3 is the so-called D3cold current state. This is always good for mobile devices. The rest of the entries are not boring either, but mainly concern Renoir and various improvements (Fine Tuning).

Kommentieren