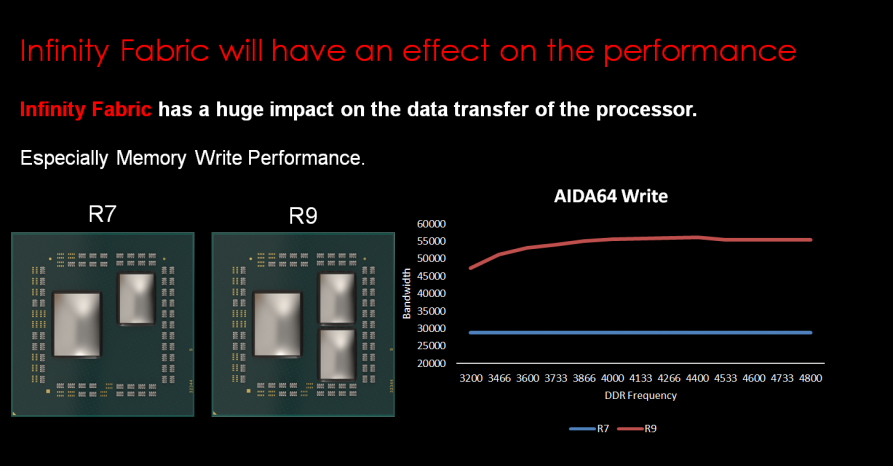

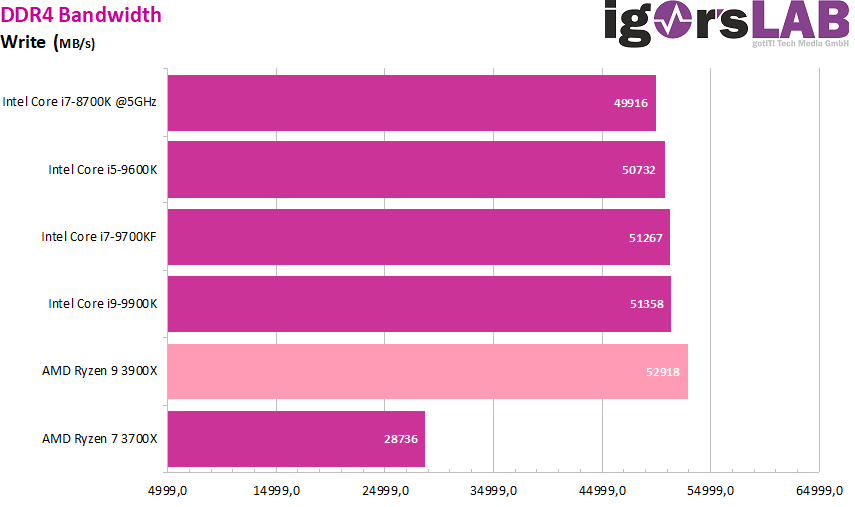

When testing the new AMD Ryzen 3000 CPUs, we found a significant difference in write rates between the R9 3900X and the R7 3700X in the aidA64 storage benchmarks. After initial astonishment and theoretical assumptions, AMD has now confirmed that it is indeed a conscious choice of architecture.

The DRAM write bandwidth of the Ryzen 3000 with a single CCD (CPU chiplet) is actually only half that of the Ryzen 3000 with two chiplets – for example, the 3900X. But what impact does this have on performance? AMD has issued an official statement saying that the observed behavior and performance difference in favor of the 3900X is normal.

Concerning AIDA 64, we didn't talk about it in the call, but one of the optimizations brought by Zen 2 is the reduction of the writing bandwidth from a CCD to the IOD from 32B/cycle to 16B/cycle when the writing bandwidth remains fully provisioned at 32B/cycle. Since workloads have little writing, the link does not need to be 32B wide. This choice of design makes it possible to optimize the surface area used but also the consumption to concentrate innovation efforts in other parts of the architecture. In other words, with the 3700X and only one chiplet the observed behavior is normal (and on 3900X with two chiplets you will logically observe higher theoretical writing results).

To save consumption and space, the DRAM write bandwidth of a CCD to the IOP is reduced from 32 bytes/cycle to 16 bytes/cycle on the Infinity Fabric. This is an approach that targets the professional applications, because workloads require fewer write accesses than read access in practice. The memory fire width remains at 32 bytes/cycle. The connection between the IOP storage controller and the DRAM is not affected by this limitation.

First, a slide from a motherboard manufacturer that addresses exactly this point is used as proof.

According to AMD, the impact on performance in practice is therefore minimal. A Ryzen 3000 with two CCDs (12 cores and 16 cores) aggregates the theoretical DRAM write bandwidth. It is therefore doubled, but still remains at 16B/cycle between each chiplet with 6 or 6. 8 computational cores and the IOP. This is also proven by our benchmarks from the launch test for Ryzen. Based on the first test runs, the smaller Ryzen 5 3600 does not appear to show this difference in speed.

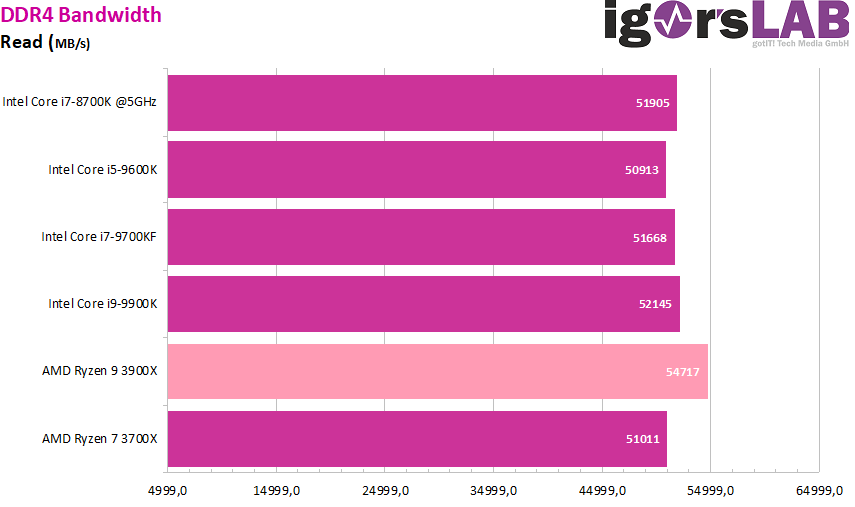

When reading, however, you don't notice anything:

This would allow the AMD Ryzen R7 3900X to become the focus of (semi-)professional users who rely on high-memory applications. These include video editing and streaming solutions that cache streams in real time.

AMD Ryzen 9 3900X, 12C/24T, 3.80-4.60GHz, boxed (100-100000023BOX)

AMD Ryzen 7 3700X, 8C/16T, 3.60-4.40GHz, boxed (100-100000071BOX)

| Lagernd im Außenlager, Lieferung 2-3 WerktageStand: 27.07.24 08:10 | 119,89 €*Stand: 27.07.24 08:12 |

| Auf Lager; Lieferzeit: 2 Werktage | 119,90 €*Stand: 27.07.24 06:49 |

| Versandlager: Lieferzeit 1-2 TageSuperstore Siegburg: nicht lagerndStand: 27.07.24 04:32 | 120,00 €*Stand: 27.07.24 04:35 |

Kommentieren