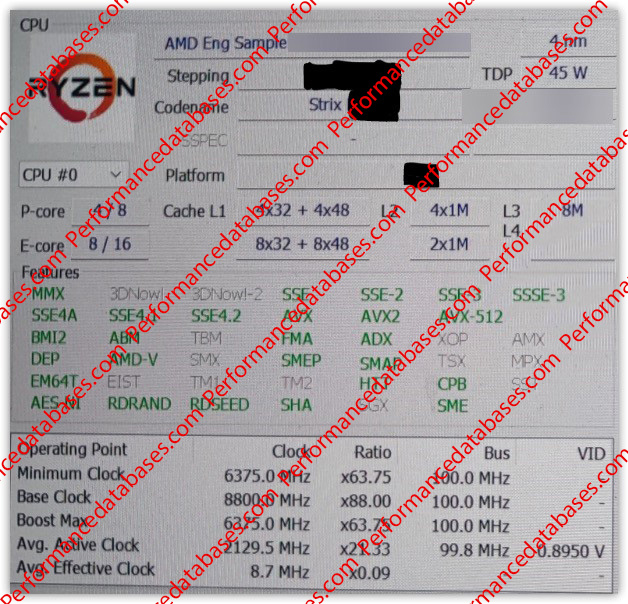

Die nächste Generation der APU, intern als “Strix” bezeichnet, wird auf einem 4-Nanometer-Prozess aufbauen. Dieser Prozess verspricht eine ausgewogene Kombination aus Leistung und Energieeffizienz. Die APU richtet sich gleichermaßen an professionelle Anwender und solche, die anspruchsvolle Unterhaltungserlebnisse suchen. Eine besonders bemerkenswerte Eigenschaft der “Strix”-APU ist ihre innovative Big.Little-CPU-Architektur. Durch die Koexistenz von 4 Performance-Kernen und 8 Efficiency-Kernen wird eine harmonische Balance zwischen Verarbeitungsleistung und Energieverbrauch angestrebt.

Diese Architektur ermöglicht der APU eine effiziente Bewältigung sowohl von rechenintensiven Aufgaben als auch von alltäglichen Anwendungen. Die Hyper-Threading-Technologie, die von beiden Kategorien der Kerne unterstützt wird, eröffnet eine erweiterte Parallelverarbeitung. Das bedeutet, dass die APU in der Lage ist, mehrere Aufgaben gleichzeitig auszuführen, was insgesamt zu einer flüssigeren und reaktionsschnelleren Leistung führt. Die Hyper-Threading-Unterstützung trägt dazu bei, die Nutzererfahrung zu optimieren, sei es bei produktiven Anwendungen mit Multitasking-Anforderungen oder beim nahtlosen Wechsel zwischen verschiedenen Anwendungen und Spielen.

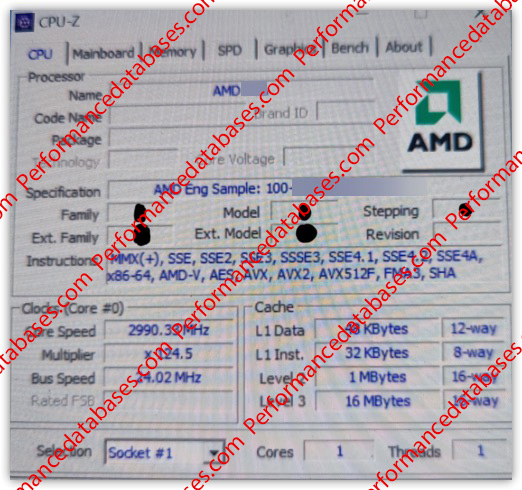

Der Cache-Speicher spielt eine wichtige Rolle für die Leistung moderner Prozessoren und APUs. Im Fall der “Strix”-APU ist der großzügige L1-Daten-Cache mit 48 KB dimensioniert, um schnelle Datenzugriffe zu ermöglichen. Dies gewährleistet eine reibungslose Bereitstellung der benötigten Daten für die Kerne. Zusätzlich steht ein 32 KB großer L1-Befehls-Cache zur Verfügung, der die effiziente Ausführung von Befehlen unterstützt und somit die Gesamtleistung steigert. Die Performance-Kerne der APU sind mit einem 1 MB Cache ausgestattet, der häufig genutzte Daten in unmittelbarer Nähe hält. Dies minimiert die Latenzzeit für den Zugriff auf diese Daten und erhöht die Gesamtleistung, besonders bei rechenintensiven Aufgaben, die schnelle Datenverarbeitung erfordern.

Die Efficiency-Kerne nutzen eine intelligente Cache-Struktur, bei der jeweils 4 Kerne einen gemeinsamen L2-Cache von 1 MB teilen. Diese Herangehensweise verbessert die Ressourcennutzung und maximiert die Energieeffizienz. Die Efficiency-Kerne sind besonders bei Aufgaben mit geringer Rechenanforderung effizient einsetzbar, um eine optimale Balance zwischen Leistung und Energieverbrauch zu erreichen. Die Ähnlichkeit des Cache-Designs mit dem von Intel zeigt, wie Technologieinnovationen über verschiedene Hersteller hinweg inspirieren können. Es ist jedoch zu beachten, dass die “Strix”-APU sich noch in der Engineering Sample-Phase (ES-Phase) befindet. In dieser Phase erfolgen weitere Entwicklungen und Optimierungen, bevor das endgültige Produkt auf den Markt kommt.

Die Entwickler sind sich dieser Dynamik bewusst und haben betont, dass sie die Öffentlichkeit kontinuierlich über den Entwicklungsprozess informieren werden. Zukünftige Updates und Fortschritte in der Entwicklung der “Strix”-APU werden transparent kommuniziert, um die Vorfreude und das Verständnis für diese technologische Innovation zu fördern. Die Welt darf gespannt sein, wie die “Strix”-APU die Computerleistung auf neue Wege führen wird.

Quelle: PerformanceDatabases

8 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Neuling

Urgestein

Urgestein

Urgestein

Mitglied

Veteran

Alle Kommentare lesen unter igor´sLAB Community →