Intel’s upcoming generation of Arrow Lake desktop CPUs could have an advantage in terms of instruction set support over their mobile Arrow Lake H siblings. According to Intel’s 50th Future ISA Guide, Arrow Lake’s ISA (Instruction Set Architecture) will be different between desktop and laptop platforms. This is because the 2nd generation Core Ultra laptops are missing some features such as AVX-VNNI-INT16 and more.

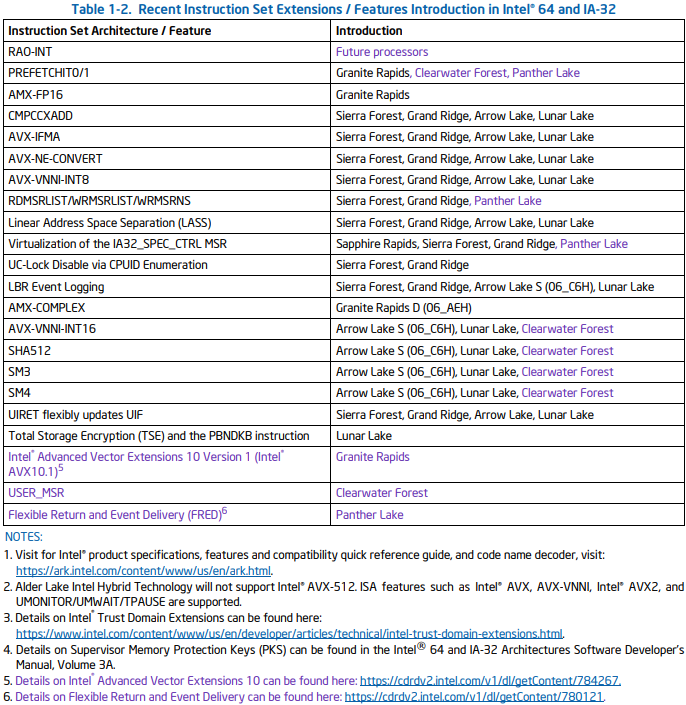

The ISA Guide is essentially a listing of instruction sets that either already exist or can be added to a CPU family from Intel. Intel has announced that the Arrow Lake desktop CPUs will include support for several instruction sets such as AVX-VNNI-INT16, SHA512, SM3 and SM4, and LBR event logging. However, these instruction sets will not be included in Arrow Lake mobile chips designed for mobile applications. Although Intel has not provided an explanation for this decision, it could be related to the applicability of the mentioned instruction sets and the core structure of both CPU families.

As far as the individual instruction sets are concerned, AVX-VNNI-INT16 is a type of “Vector Neural Network Instructions” aimed at completing machine learning and artificial intelligence tasks much faster. The fact that these will be missing from the Arrow Lake-H mobile chips would result in significantly lower performance for AI-related workloads compared to the Arrow Lake-S parts. However, for the average user who is not interested in AI, this would have little impact on mainstream applications. Therefore, consumers who do not use AI applications should not worry about it.

According to the 50th Future ISA Guide, this time #ArrowLakeH C065x mobile has different ISA than the #ArrowLakeS C066x desktop#AVX_VNNI_INT16, #SHA512, #SM3, #SM4 https://t.co/5nUqDcnoDl pic.twitter.com/Yf1dvLBNOY

— InstLatX64 (@InstLatX64) October 30, 2023

The SHA512, SM3, and SM4 cryptographic instruction sets are also designed to improve algorithm performance and enhance onboard security. Hardware support for these algorithms enables the processor to perform hash calculations and encryption/decryption operations much faster than software-based implementations. In addition, all Arrow Lake chips will also include some instruction sets, such as CMPCCXADD, AVX-IFMA, AVX-NE-CONVERT, RDMSRLIST, LASS and UIRET.

It is assumed that the Arrow Lake-S CPUs will be developed by Intel for dual-core architectures, namely Lion Cove for P-cores and Skymont for E-cores. In contrast, Arrow Lake-H and mobile chips will use a three-core architecture, with Lion Cove for P-cores, Skymont for E-cores and Crestmont for energy-efficient E-cores that remain on the I/O tile. However, since Crestmont does not support the latest ISA, Arrow Lake H-chips will not be able to take full advantage of the latest ISA. This coincides with earlier reports that mentioned Meteor Lake and Arrow Lake chips with a very similar VPU, while Lunar Lake is expected to receive a major update.

It is known that Intel might add instruction sets to a certain product line in the future. Therefore, support for such instruction sets from the company is never final. So, there is a possibility that Arrow Lake Mobile CPUs can also benefit from these instruction sets in the future.

Source: @InstLatX64

2 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Veteran

Alle Kommentare lesen unter igor´sLAB Community →