@RX480:

Ich vermute wenn Intel mit RDNA4 mithalten können wird, können sie schon froh sein, jedoch bei Intel ist aktuell unklar, wie groß deren Entwickungschritt ausfallen wird, da hier zu viele Unbekannte im Spiel sind. Hier gibt es keinerlei Historie weil Alchemist die 1st Gen ist, man weiß nicht welche (wirtschaftliche) Zielsetzung sie haben und man kann bestenfalls vermuten, dass noch einige Verbesserungen ggü. der ursprünglichen Planung hinzugekommen sein

könnten, da Battlemage ursprünglich mal als 2023-Produkt geplant und für 2024 bereits Celestial vorgesehen war. Hinzu kommen weitere Unbekannte aufgrund der internen Reorganisation und man weiß nicht so genau, wie viel Prio sie dem Projekt wirklich zuordnen. Vielleicht sieht man auch keine Synergieeffekte mehr zwischen der Consumer- und HPC-Entwicklung (?), sodass man das Engagement im Consumer-Segment wieder zurückgefahren hat?

Treibertechnisch würde ich mir keine allzu großen Sorgen mache, da die stetige Vebesserungen vorstellen können und zumeist bleibt zu vermuten, dass weniger Intel als eher die Entwickler das Problem sind, die nicht strikt DX-konform implementieren, sodass deren Treiberteam hier viel Kompensationsarbeit leisten muss. Wenn man Pech hat, ist das aber ein Henne-Ei-Problem, d . h. eine höhere Aufmerksamkeit durch die Entwickler erst bei größeren Marktanteilen aber um diese zu erreichen bedarf es wiederum guter Leistung, die eigentlich die Unterstützung der Entwickler bedarf ... und hier muss dann halt (vorerst übermäßig) Intels Treiberteam einspringen.

Wenn man will, könnte man zumindest das hohe Engagement in der Treiberentwicklung so werten, dass Intel seine Consumer-Entwicklung keinesfalls aufs Abstellgleis schieben will, dagegen wie weit dieses Indiz dafür herhalten kann um die tatsächlich Höhe deren Engagements bzw. der Priorität des Consumer-GPU-Projekts abzuschätzen, ist unklar.

*) Ergänzend, Intel

könnte auch durchaus überraschen, denn die arbeiten schon von Anfang an auch an MCM-Designs im GPU-Bereich, auch mit Blick auf Consumer-GPUs. Jedoch würde ich aufgrund der Wirtschaftlichkeit mit Blick auf Battlemage eher nicht von einem entsprechenden Produkt ausgehen, vielleicht bei Celestial in 2026+ ? Hätte Intel AMDs Fail bei RDNA4 jedoch vorhersehen können, wer weiß, vielleicht hätten sie hier alles dran gesetzt das schon mit dem repositionierten 2024er-Battlemage in den Markt zu bringen, denn damit hätte man AMD leicht komplett ausboten können, aber das sind eher weniger absehbare, bzw. hochspekulative Ereignisse, die man eher nicht einplant.

Zum Thema gestapeltem Cache bei GPUs: Hier ist die Frage wie und wo man das implementiert. Direkt auf dem GCD macht es keinen Sinn weil hier die Verlustleistung viel zu hoch ist und das zusätzliche Silizium die Wärmeabfuhr beträchtlich einschränkt, sodass man früher in ein thermisches Limit läuft, was wiederum den Takt beschränkt.

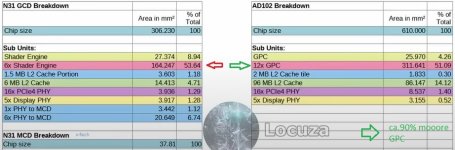

Würde man die Speichercontroller in Form des MCD weiterhin auslagern, könnte man diesen darauf stacken, jedoch ist auch hier die Frage ob das einen echten Kosten-/Nutzen-Vorteil bieten würde, vermutlich eher nicht. So gab es anscheinend einen entsprechenden RDNA3-Prototypen, im Labor, dem eine "

abysmal cost to benefit ratio" nachgesagt wurde. Hierbei ist zu berücksichtigen, dass man zusätzliches Silizium und damit Wafer-Fläche benötigt und weiterhin zusätzlich benötigt man auch noch teueren und zudem knappen Packaging/Stacking-Prozess und das nicht nur 1x (

wie bspw. ein einem Ryzen) sondern bspw. bei Navi31 gleich für ganze sechs Chips unb man könnte das Produkt dennoch nicht übermäßig hochpreisig verkaufen, weil man AMD bei ihrem derzeitigen Entwicklungsstand solche Produkte einfach nicht abnimmt.

Zudem wird das Stacking vermutlich auch nicht übermäßig viel bringen, da einen schon grundsätlzich großen Cache noch ein wenig größer auszulegen (

dafür aber auch mit etwas schlechterer Latenz) bringt i. d. R. eher wenig.

Vermutlich wird hier das erfolgversprechendere Rezept sein den L3$ im MCD behutsam zu vergrößern (wenn überhaupt?) und ergänzend schnelleres GDDR anzubinden. Am Ende ist der L3$ als Einzelkomponente per se komplett irrelevant und es geht hier lediglich um die insgesamt bereitgestellte Speicherbandbreite. Letzten Endes muss man berücksichtigen, dass der zusätzlich L3$ auf RDNA bisher lediglich den Zweck hatte ein komplexeres und damit teueres SI zu vermeiden und weil man keinen Zugang zu schnellem GDDR6 hatte, d. h. hätte man regulär auf Speicherbandbreite XY kommen wollen, hätte man das SI noch weiter verbreitern und noch mehr Speicherchips anbinden müssen, was zusätzliche Controller, PHY (damit Wafer-Fläche) und Verlustleistung und Speicherchips und insgesamt Kosten mit sich gebracht hätte.

*) Zum Gegenvergleich, nVidia hat sich dagegen entschieden und mit schlicht seinen L2$ zu vergrößern und offensichtlich eine gute Wahl getroffen. In Verbindung mit dem weiterhin monolithischen Design und dem deutlich breiteren Absatzmarkt wird man hier weitaus profitabler unterwegs sein als AMD und konnte sich bisher die unnötige Komplexität und Komplikationen eines MCM-Designs ersparen und konnte gar noch das leistungsfähigere und effizientere Design abliefern. - Unschön nur, dass der Platzhirsch derart alleine auf weiter Flur steht und dementsprechend auch freie Hand bei der Preisgestaltung hat. ;-)