@

Deridex: "

Ein Drop-In-Replacement bedeutet nicht, dass nichts verändert wurde ...", nun das war auch Deine Behauptung; Ich selbst habe doch bereits rein in Verbindung mit dem Speichersubsystem auf einige Veränderungen hingewiesen

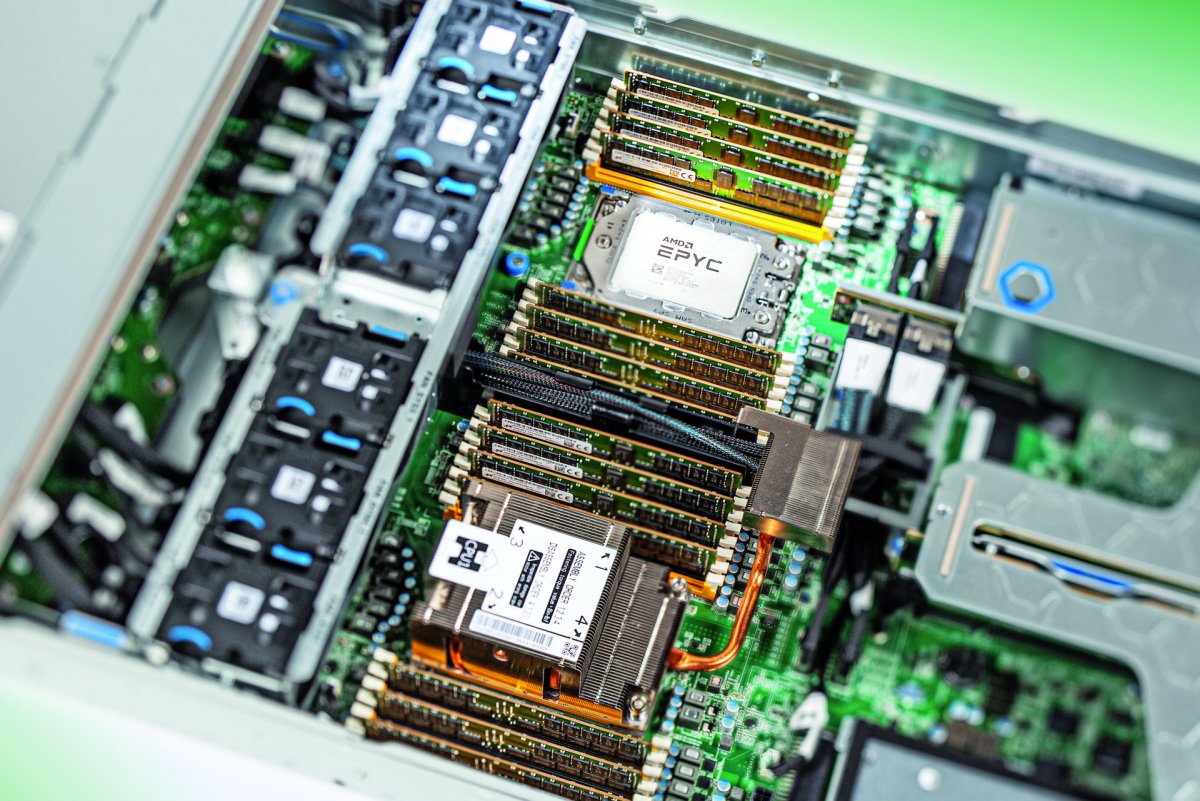

Aber am grundsätzlichen Setup, 8-Kanäle, DDR4, etc. hat sich nichts verändert und der Durchsatz steigert sich nur insofern, als dass jetzt DDR4-3200 möglich ist, sowie verbesserte (und Latenz-kompensierende) Caches (in einem Dual-Socket-System effektiv nicht ganz +10 % ggü Naples, für den Rest, s. u. ).

@

Besterino: Ah, das meintest Du. An den alten TR habe ich schon gar nicht mehr gedacht a) weil technisch ungünstig gelöst (bei > 16 Kernen), aber zu der Zeit nun mal so erforderlich und b) wir gerade über Zen2 reden.

Aber das erklärt, warum Du mir eine "sportliche Ansage" unterstellst, obwohl ich zum Speicherinterface von TR (weder alt noch neu) überhaupt keine Aussage getroffen habe.

Der neue TR wird analog Epyc dessen 14nm-IOD verwenden und damit sollten sich dann alle Fragen von selbst klären, oder?

Im Detail: AMD verwendet zwei IOD-Desings, den keinen 12nm-Chip für die Consumer-Produkte und den großen 14nm-Chip (der auch flächentechnisch deutlich größer ist) für Epyc. Da AMD sehr effizient bei der Entwicklung/Fertigung ist (bzw. sein muss) werden sie bestimmt keine kaum/selten benötigte Funktionalität in den Consumer-IOD implementieren (bspw. 4-Kanal-Speicher, und vielfache Anschlussmöglichkeiten von CCDs), zumal diese Implementation doppelte Arbeit darstellen würde, da sie diese bereits im größeren IOD implementiert haben. (Würde man das annehmen, hätten sie sich ein zweites Design von vornherein sparen können, denn auch einen IOD zu entwickelten kostet beträchtliche Ressourcen. ) Zudem stellt sich die Frage ob man flächentechnisch an den kleinen IOD überhaupt so viele Leitungen heranführen kann, sodass 4 - 8 CCDs *) angeschlossen werden könnten; sieht man sich den Package-Shot von Ryzen an, wurde ich sagen nein, das geht nicht.

Also, TR nutzt den 14nm-IOD von Epyc, man deaktiviert vier Speichercontroller und einige andere Kleinigkeiten, wie bspw. SEV und schon hat man einen TR, der in der Zen2-Iteration noch einmal mehr einem Epyc gleicht. Wie bei Zen2 grundsätzlich, läuft jedwedes I/O über den IOD und damit entfallen auch die Probleme, die man bei der letzten Generation bei der Verwendung von > 16 Kernen beobachten konnte.

Von daher sind Spekulationen zur TR-Performance auch wenig "erquickend", da man sie (bis auf den Takt, das hatten wir schon zuvor) vom Epyc ableiten kann. Die Rechenleistung der Kerne ist bekannt (Ryzen, Epyc, alles das gleiche CCX-Design inkl. L3), die Kommunikation läuft per IF über den IOD und hier sind lediglich 4 Speicherkanäle zu subtrahieren (ggü. Epyc oder 2 Kanäle hinzuzuaddieren im Vergleich zu Ryzen; es verbleiben vielleicht noch Fragen zu den PCIe-Lanes und der sonstigen Konnektivität).

Trivia am Rande: AMD verwendet den 14nm-IOD auch für den Epyc-Chipsatz/PCH. Hier deaktviert man lediglich einige Funktionen wie bspw. die Speichercontroller und schon hat man den PCH. Das kann man wirklich effizient nennen. Wie es beim TR aussehen wird, bleibt abzuwarten, denn die Frage ist, ob AMD mit Weitsicht und Blick auf TR den IOD mit umfangreichem USB/SATA-Support ausgestattet hat (ganz ohne kommt auch ein Epyc nicht aus) oder ob man hier vielleicht den X570 zum X599 umarbeitet oder gar nur umbennent. **)

*) Da ein Chiplet (CCD) bestenfalls zwei CCXe aufweist, muss ein TR bereits mindestens 4 CCDs an seinem IOD anbinden können und wäre damit immer noch auf 32 Kerne beschränkt, sodass L.Su's Aussage "

if Ryzen goes up, TR also has to go up" nicht zutreffen würde. Für mehr als 32 Kerne sind also auch mehr als 4 CCDs erforderlich und das ist schlicht zu viel Platzbedarf am IOD, siehe die weißen Kontaktierungen des IF bei

AnandTech (unten) mit nur zwei CCDs (3900X oder 3950X). Am 12nm-IOD bleibt einfach kein Platz für ein solches Vorhaben.

Hinzu kommt der Punkt, dass AMD zumindest bei Epyc auch Modellvarianten anbietet, die ein deutlich abweichendes Chiplet/Kernverhältnis aufweisen, so zu sehen an den 128 MiB-Varianten 7262 und 7302. Letzterer besitzt bspw. "nur" 16 Kerne, verwendet jedoch vier CCDs, sodass er 128 MiB L3 hat, d. h. hier haben die CCXe nur jeweils zwei aktive Kerne. Im Gegensatz dazu verwendet der 7282 mit ebenfalls 16 Kernen nur zwei CCDs und ist auch gleich deutlich günstiger (650 US$ ggü. 978 US$ laut Listenpreis).

Epcy und TR könnten durchaus aus Stabilitätsgründen bzgl. des CPU-Packages wieder aus min. 4 CCDs/Chiplets bestehen. Für den 7282 würde das bedeuten, dass auf diesen vier CCDs irgendwo vier vollständige CCXe aktiv sind, während alle übrigen CCXe komplett deaktiviert sind.

**) Schlussendlich eine Frage der anfänglichen Planung. Wo kann man die die Funktionalität, die die Plattformen unterscheidet, am effizientesten unterbringen? Unterm Strich würde ich gar eher zum Die tendieren, das jetzt schon für den X570 genutzt wird. Vielleicht wurde dieses gleich von Beginn an mit Blick auf TR konzipiert und es gibt gar keine nennenswerten Unterschiede am PCH. Wie die MB-Hersteller die zur Verfügung gestellten Ressourcen nutzen, bleibt ihnen eh überlassen. Hinzu kommt auch die Möglichkeit, dass man einige, wenige Spezialfunktionen mittels zusätzlicher Chips anbinden kann (zu viele Zusatzchips und das Boarddesign wird zu teuer; andererseits, wenn man sich die Preise der X570er Boards ansieht, spielt das wohl kaum eine Rolle, den 170 €-Boards sind hierbei schon die absoluten Schnäppchen

)