Intel’s IMPV9.1 for Alder Lake S and Raptor Lake S

For those who don’t know, IMPV, or Intel Mobile Voltage Positioning, is a technology that dynamically adjusts the processor voltage (VCC) based on processor activity to reduce the power consumed. It allows a higher processor clock frequency for a given power consumption or a lower consumption for a given clock frequency, as the case may be. The new iteration IMP9.1 introduced with Alder Lake S is not a real revolution compared to IMPV9 from Rocket Lake S, but it is an important iteration that improves many details.

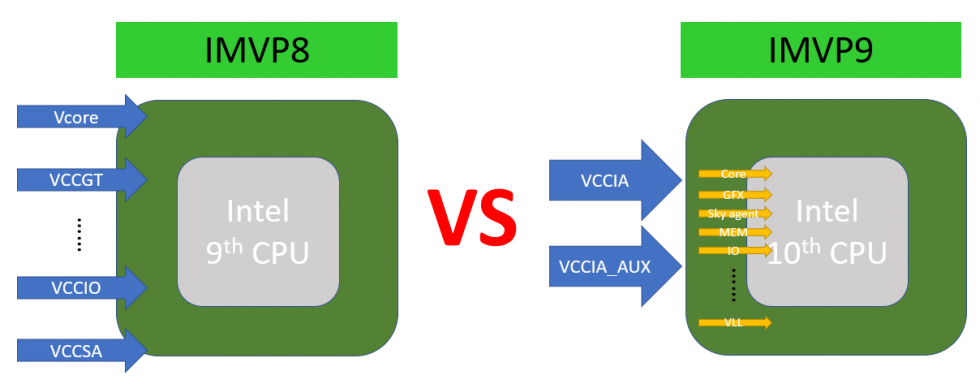

New is the support of two VID tables with 5 mV and 10 mV resolution and the support of Iout with values above 255 Amps. In addition, there is an analog AUX imon input on the 0x0Dh domain. There is also a change to the fast Psys counters and peak detector to support both Psys and Vsys measurements independent of the old Psys ADC input. IMPV9 was already used for the 10th generation and it was a big step forward compared to IMPV8, which we still know from the CPUs of the 9th generation.

We’ll keep this graphic in mind for the next page, even if there are lines added for Raptor Lake S that have not yet been drawn here.

The PL4 and the innovations

It also changes the PS4 performance definition: processor Pmax, Never Exceed and Limit. All this is calculated “a priori” and is therefore a real PROACTIVE limit (through differentiated advance planning and targeted interventions, the result itself is planned and achieved). PL1 and PL2 refer only to the average power (see table and graph above) and are REACTIVE limit values where only values can be reacted to retrospectively. The mysterious PL4 referred to peak power events, which could only be handled PROACTIVELY in the past and often never turned out quite optimal in the end.

A new, REACTIVE PL4, on the other hand, is the ideal solution, keeping SoC frequencies as high as possible, but with a safety net based on Fast PROCHOT#. This is a digital output pin that has been around since Intel’s Pentium 4 processors and indicates that the internal thermal control circuit has been activated. This occurs when the processor has reached its maximum safe operating temperature. The SoC frequency is still determined by the PL4.

When PROCHOT# is enabled, the total power of the SoC is always BELOW PL4_Safe, i.e., less than the value specified for the PL4. PL4_Safe thus represents the level of peak power that the input power sources can deliver without fear of brownout or damage to the battery, or generally overloading the supply and the interconnected components, for example in the notebook sector. Fast PROCHOT# is really fast. Vsys1 is monitored by the IMPV9.1 controller and PROCHOT# is activated within 2 μs (adjustable) after the threshold is exceeded. The CPU is then already throttled 1μs later. Fast PROCHOT# thus allows for a higher PL4, resulting in better responsiveness down to low load conditions while maintaining system stability, but also produces harsher load changes.

However, one of the most important pieces of information is the interval of PL4. Here this state can last up to 10 ms, but never longer.

This is also extremely important for the dimensioning of the protection circuits in the power supply. The 10 ms are quite a challenge and many a power supply will have to be redesigned in this respect. Companies such as be quiet! have been using an interval of 20 ms for years, so here you should rather be on the safe side if the current can also be delivered. We will see how high the PL4 really is for Alder Lake S and also Raptor Lake S then on the next page.

The Potential Peak Power (PPP)

The PPP is an expected worst-case power level calculated by the Power Control Unit (PCU) based on component characteristics and the current operating frequency (IA, GT, ring domains). This happens before each frequency transition (usually at 1-ms boundaries), or whenever AVX instructions enter the pipeline or when a core C state change is imminent. PPP assumes a scenario across domains that is the most intensive known application.

So what does this mean in the context of the PL4? Very simple: the PL4 is the limit value to which PPP is finally compared! If PPP is > PL4 at the frequency transition, a lower frequency is selected to prevent PPP from exceeding PL4. PPP is in the by the way a pure projection and is NOT based on the power telemetry of the actual workload. The PPP projection is also not displayed via a software interface, but only used within the PCU.

The absolute peak power can thus only be reduced preventively via the PL4 settings.

And after we’ve had a little bit of a look through the terms, you’ll now also find on the next page the detailed performance figures and compatibility comparison between Alder Lake S and Raptor Lake S, which will also share the motherboard over two generations, whereby upward and downward compatibility should be given here.

Kommentieren