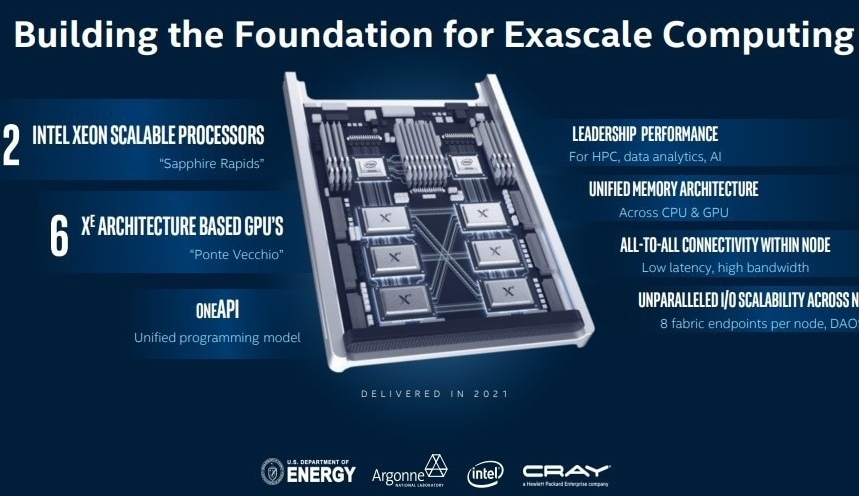

Sometimes it is good to wait at least a day or two to check the validity of some reports. For example, DigiTimes reported the day before yesterday that Intel had booked 180,000 wafers in the 6 nm process at TSMC and would use them for their flagship HPC GPU Ponte Vecchio. The order and the quantity should be right in the end, but the targeted product behind it is a completely different one. Intel’s Ponte Vecchio GPU will therefore not be produced by TSMC using the 6 nm process. Instead, the GPU will be manufactured in both TSMC’s 5 nm process and Intel’s 7 nm process. Thanks for this information go to my colleague Usman Pirzada from wccftech.com , who in the meantime had the opportunity to talk to the right people.

Intel’s Ponte Vecchio GPU is the company’s upcoming flagship when it comes to discrete graphics and the Aurora supercomputers. Not surprisingly, investors were initially startled to hear Intel’s CEO announce that the company would rely more on TSMC to complement its own foundries for the time being. Obfuscated publications then erroneously state that Intel’s Ponte Vecchio GPU is to be manufactured in TSMC’s 6nm process, which is surprising, since T6 is essentially an optimized variant of T7, which in effective density then corresponds approximately only to Intel’s 10nm process. However, such a shift would drastically worsen the performance profile of Intel’s upcoming GPU.

So Usman turned to a number of sources in Taiwan and got the facts first hand from people directly involved in the production of this GPU. In summary, it reads like this:

- TSMC’s 5 nm process is roughly comparable in density to Intel’s 7 nm process, and this GPU is only feasible at this density level – so 6 nm (which is an optimized process for TSMC’s 7 nm) is out of the question.

- Ponte Vecchio will have several SKUs.

- Intel produces an IO die for all Ponte Vecchio SKUs.

- Depending on the SKU, either Intel’s 7nm process or TSMC’s 5nm process is used.

- The Rambo cache is also produced internally at Intel.

- The Connectivity Die (Intel Xe) was originally intended to be established at TSMC and will remain there.

- Although Intel has placed an order worth 180,000 wafers in TSMC’s 6 nm process, this order is not related to Ponte Vecchio but is part of the ongoing partnership (Intel has been using TSMC for some time).

The Taiwanese newspaper was right about the wafer order, but they were wrong in assuming that it was Ponte Vecchio. This order therefore has nothing at all to do with Ponte Vecchio, since this GPU requires a process with a density greater than TSMC’s 7 nm/6 nm or Intel’s 10 nm is What the large number of wafers ordered is now needed for, then falls back into the realm of speculation.

The fact that Intel’s 7-nm process is stalling a bit and will probably continue to be delayed was also evident over the past few days, and so the winner is once again TSMC. You could bet that Intel’s Ponte Vecchio would first come off the assembly line at TSMC before Intel’s own foundries would finally run as originally planned.

Kommentieren